# **WARNING**

THE FOLLOWING SERVICING INSTRUCTIONS ARE FOR USE BY QUALIFIED PERSONNEL ONLY. TO AVOID PERSONAL INJURY, DO NOT PERFORM ANY SERVICING OTHER THAN THAT CONTAINED IN OPERATING INSTRUCTIONS UNLESS YOU ARE QUALIFIED TO DO SO.

PLEASE CHECK FOR CHANGE INFORMATION AT THE REAR OF THIS MANUAL.

# 7912AD PROGRAMMABLE DIGITIZER SERVICE VOL. 1

INSTRUCTION MANUAL

Tektronix, Inc.

P.O. Box 500

Beaverton, Oregon 97077

Serial Number \_

070-2407-00 Product Group 45

First Printing APR 1979 Revised APR 1984

# Scans By *Artek Media*

Artek Media 1042 Plummer Cir. SW Rochester, MN 55902

www.artekmedia.com

"High resolution scans of obsolete technical manuals"

If your looking for a quality scanned technical manual in PDF format please visit our WEB site at <a href="www.artekmedia.com">www.artekmedia.com</a> or drop us an email at <a href="manuals@artekmedia.com">manuals@artekmedia.com</a> and we will be happy to email you a current list of the manuals we have available.

If you don't see the manual you need on the list drop us a line anyway we may still be able to point you to other sources. If you have an existing manual you would like scanned please write for details, This can often be done very reasonably in consideration for adding your manual to our library.

Typically the scans in our manuals are done as follows;

- 1) Typed text pages are typically scanned in black and white at 300 dpi.

- 2) Photo pages are typically scanned in gray scale mode at 600 dpi

- 3) Schematic diagram pages are typically scanned in black and white at 600 dpi unless the original manual had colored high lighting (as is the case for some 70's vintage Tektronix manuals).

If you purchased this manual from us (typically through our Ebay name of ArtekMedia) thank you very much. If you received this from a well-meaning "friend" for free we would appreciate your treating this much like you would "share ware". By that we mean a donation of at least \$5-10 per manual is appreciated in recognition of the time (a manual can take as much as 40 hours to reproduce, book, link etc.), energy and quality of effort that went into preserving this manual. Donations via PayPal go to: <a href="manuals@artekmedia.com">manuals@artekmedia.com</a> or can be mailed to us the address above.

Thanks Deep & Synneth

Dave & Lynn Henderson

Artek Media

Copyright © 1979 Tektronix, Inc. All rights reserved. Contents of this publication may not be reproduced in any form without the written permission of Tektronix, Inc.

Products of Tektronix, Inc. and its subsidiaries are covered by U.S. and foreign patents and/or pending patents.

TEKTRONIX, TEK, SCOPE-MOBILE, and registered trademarks of Tektronix, Inc. TELEQUIPMENT is a registered trademark of Tektronix U.K. Limited.

Printed in U.S.A. Specification and price change privileges are reserved.

### **INSTRUMENT SERIAL NUMBERS**

Each instrument has a serial number on a pañel insert, tag, or stamped on the chassis. The first number or letter designates the country of manufacture. The last five digits of the serial number are assigned sequentially and are unique to each instrument. Those manufactured in the United States have six unique digits. The country of manufacture is identified as follows:

| B000000 | Tektronix, Inc., Beaverton, Oregon, USA               |

|---------|-------------------------------------------------------|

| 100000  | Tektronix Guernsey, Ltd., Channel Islands             |

| 200000  | Tektronix United Kingdom, Ltd., London                |

| 300000  | Sony/Tektronix, Japan                                 |

| 700000  | Tektronix Holland, NV, Heerenveen,<br>The Netherlands |

# TABLE OF CONTENTS

# VOL. I

# SAFETY SUMMARY

# PREFACE

| SECTION 1 INTRODUCTION         | 1–1  |

|--------------------------------|------|

| The Scan Converter             | 1-2  |

| TV Mode                        | 1-5  |

| Digital Mode                   | 1-6  |

| Options                        | 1-7  |

| Option 4                       | 1-7  |

| Option 9                       | 1-8  |

| Option 13                      | 1-8  |

| Option 30                      | 1–8  |

| Specifications                 | 1–8  |

| SECTION 2 OPERATION            | 2-1  |

| Controls and Connectors        | 2-1  |

| Front Panel                    | 2-1  |

| Rear Panel                     | 2-4  |

| Operating the 7912AD           | 2-9  |

| Plug-Ins                       | 2–9  |

| Supplying Power                | 2-11 |

| Waveform Monitors              | 2-12 |

| Getting a Picture (TV Mode)    | 2-13 |

| Storing the Waveform Displayed | 2-14 |

| in TV Mode                     |      |

| Local Control in an IEEE 488 System    | 2-15          |

|----------------------------------------|---------------|

| Taking Control                         | 2-15          |

| Graticule-Only Mode                    | 2-16          |

| XYZ Outputs                            | 2-16          |

|                                        |               |

| Acquiring Data                         | 2-17          |

| Defects                                | 2-17          |

| Sweep Speed and Intensity              | 2–18          |

| Programming the 7912AD                 | 2-21          |

| IEEE Interface Function Subsets        | 2-21          |

| Addressing                             | 2-21          |

| Remote/Local Function                  | 2-23          |

| Local                                  | 2-23          |

| Remote                                 | 2-24          |

| Lockout                                | 2-24          |

| Remote Control Messages                | 2-25          |

| Input Buffering and Execution          | 2-25          |

| Command Syntax                         | 2-26          |

| Numbers                                | 2-28          |

| Set Commands                           | 2-28          |

| Query Commands                         | 2-29          |

| Response to Interface Control Messages | 2-34          |

| Error Handling                         | 2 <b>-</b> 36 |

| Command or Execution Error             | 2-36          |

| Internal Error                         | 2-36          |

| Power Fail Error                       | 2 <b>-</b> 36 |

| Status Byte                            | 2-39          |

| Device Dependent Status                | 2-40          |

| Normal Condition System Status         | 2-40          |

| Abnormal Condition System Status       | 2-40          |

| Wave        | eform Data I/O                        | 2-41          |

|-------------|---------------------------------------|---------------|

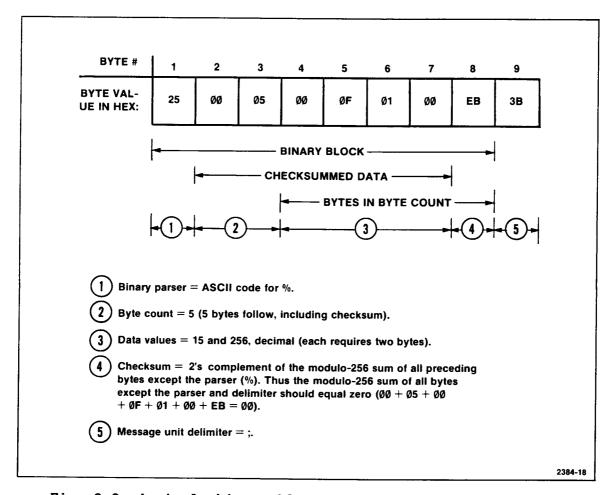

|             | Block Binary Format                   | 2-42          |

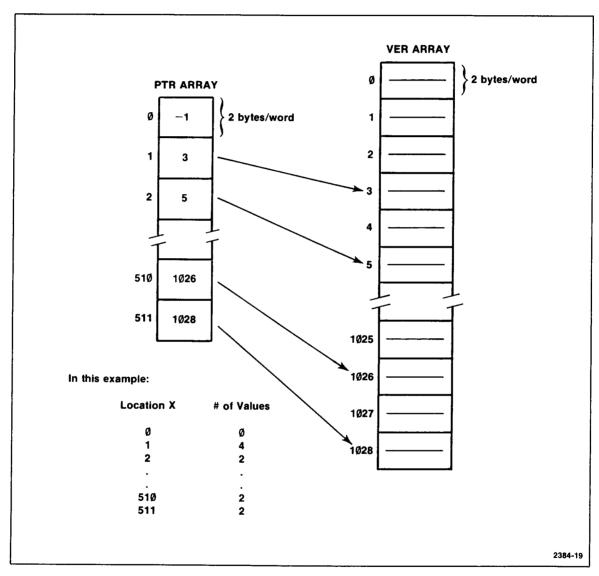

|             | READ PTR, VER and REP Commands        | 2-42          |

|             | READ ATC                              | 2-45          |

|             | READ SA                               | 2-46          |

|             | READ EDGE                             | 2-47          |

|             | READ DEF                              | 2-47          |

|             | LOAD                                  | 2-47          |

|             | DUMP RAW                              | 2-48          |

|             | DUMP PR                               | 2-49          |

| Scal        | ing the Output Waveform               | 2-50          |

| Prog        | ramming Reports                       | 2 <b>-</b> 51 |

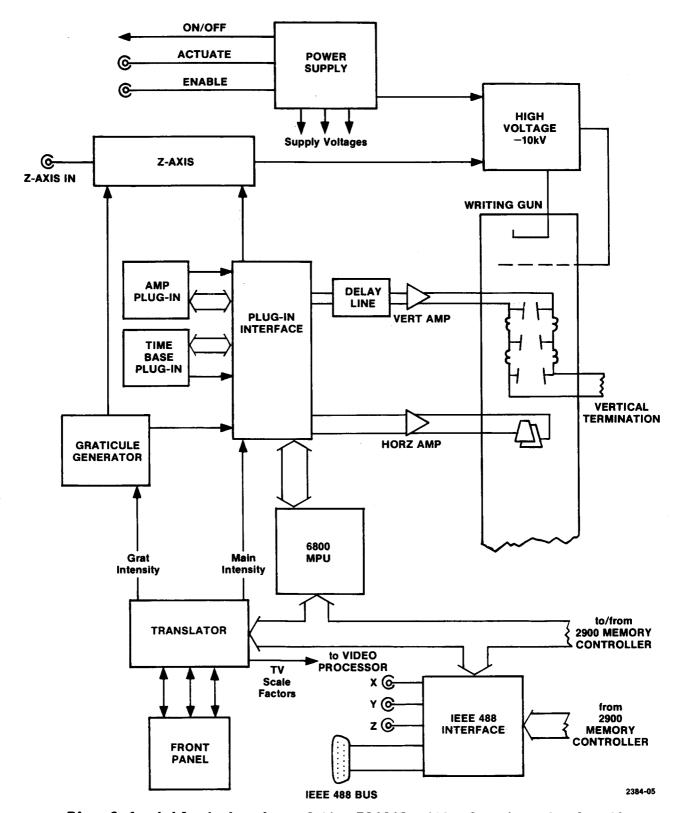

| SECTION 3 - | BLOCK DIAGRAM AND CIRCUIT DESCRIPTION | 3-1           |

|             | Power Supply                          | 3-1           |

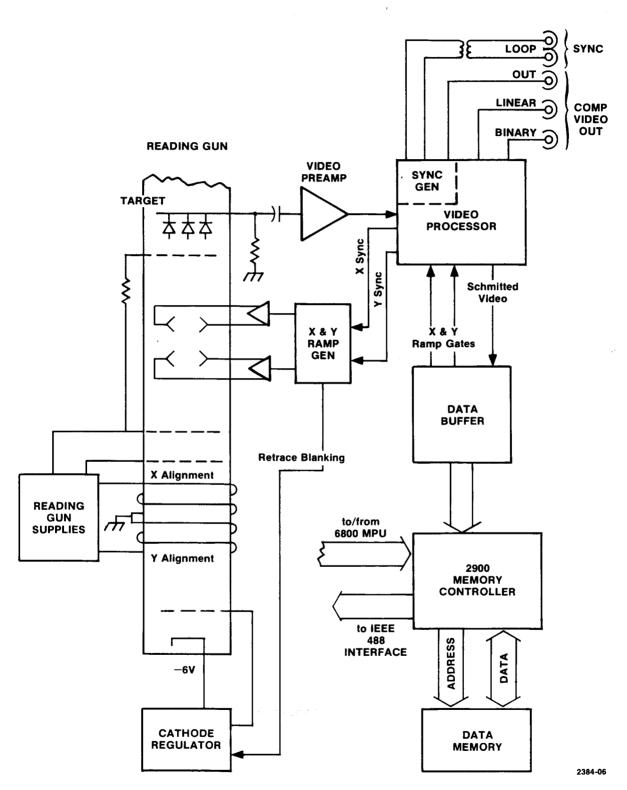

|             | Analog Signal Flow                    | 3-1           |

|             | Data Flow                             | 3-4           |

|             | Instrument Control                    | 3 <b>-</b> 5  |

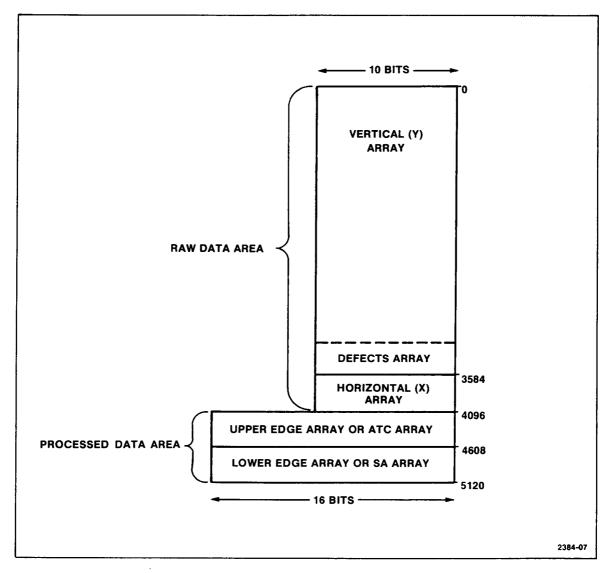

| Wave        | form Storage                          | 3 <b>-</b> 5  |

|             | Raw Arrays                            | 3 <b>-</b> 5  |

|             | Processed Array                       | 3-7           |

| Writing S   | ystem                                 | 3-8           |

| Plug        | -In Interface                         | 3-8           |

|             | Trigger Buffer                        | 3-8           |

|             | Vertical Chop                         | 3 <b>-</b> 8  |

|             | Alternate Drive                       | 3-9           |

|             | Holdoff                               | 3-9           |

|             | Sweep Gate                            | 3-9           |

|             | Z-Axis Logic                          | 3 <b>-</b> 9  |

|             | Single Sweep                          | 3-10          |

|             | Readout/7K Acquisition                | 3-10          |

| Graticule Generator                     | 3-10          |

|-----------------------------------------|---------------|

| Introduction                            | 3-10          |

| Overview                                | 3-11          |

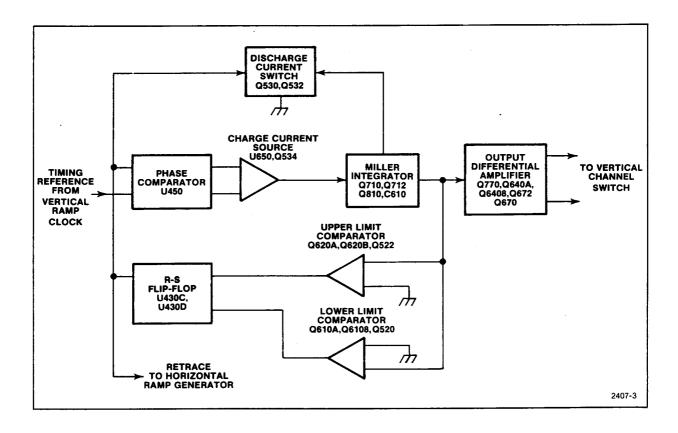

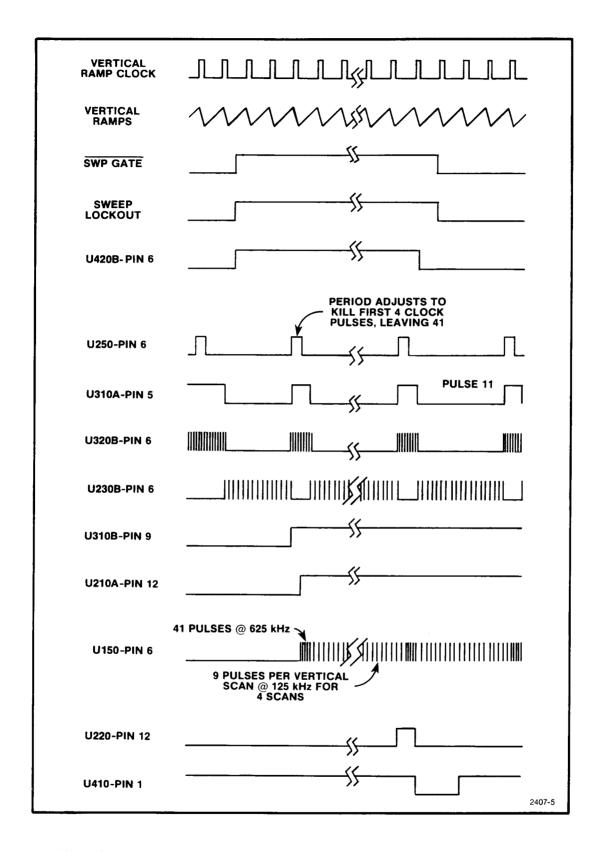

| Vertical Ramp Clock                     | 3-11          |

| Vertical Ramp Generator                 | 3-12          |

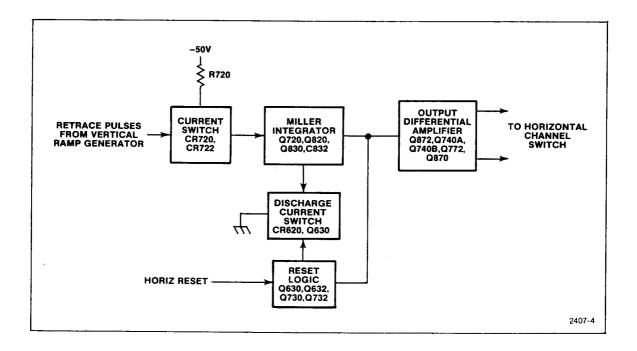

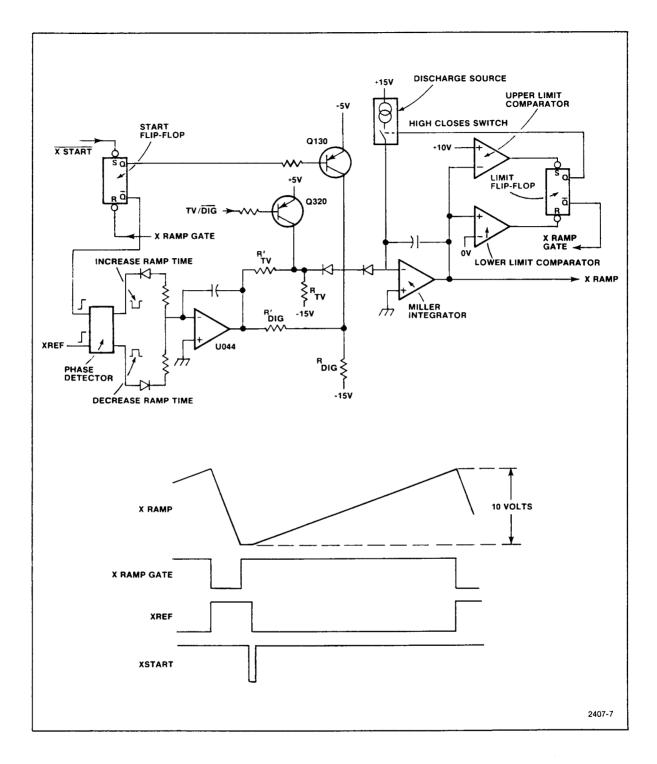

| Horizontal Ramp Generator               | 3-14          |

| Graticule Startup Logic                 | 3-16          |

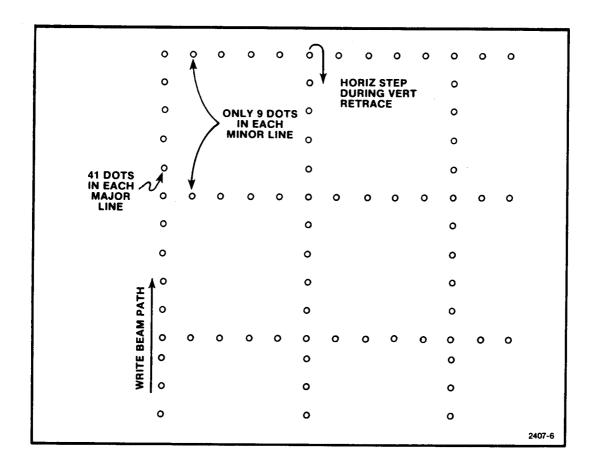

| Generating a Graticule                  | 3-18          |

| Vertical Channel Switch and Amplifier   | 3-21          |

| Vertical Channel Switch                 | 3-21          |

| High-Frequency Amplifier                | 3-21          |

| Output Amplifier                        | 3-22          |

| Horizontal Channel Switch and Amplifier | 3-22          |

| Overview                                | 3-22          |

| Horizontal Channel Switch               | 3-22          |

| Input Amplifier                         | 3-23          |

| Driver and Output Amplifiers            | 3-24          |

| Z-Axis and High Voltage                 | 3-24          |

| Overview                                | 3-24          |

| High Voltage Supply                     | 3-24          |

| -10 Kilovolt Supply                     | 3 <b>-</b> 25 |

| Blanking and D.C. Restoration           | 3 <b>-</b> 25 |

| Protecting the Circuit                  | 3-26          |

| Focus Supply                            | 3 <b>-2</b> 6 |

| Regulating the Hihg-Voltage Supply      | 3 <b>-</b> 26 |

| Z-Axis Amplifier                        | 3-27          |

| Input Circuits                          | 3-27          |

| Positive Signal Excursions              | 3-27          |

| Negative Signal Excursions              | 3-27          |

| Current Source                          | 3-27          |

| Feedback                                | 3-28          |

| Target Protection Circuit     | 3-28          |

|-------------------------------|---------------|

| Protection Threshold          | 3 <b>-</b> 28 |

| Deflecting the Beam           | 3-29          |

| Disabling BEAMFINDER          | 3-29          |

| Reading System                | 3-30          |

| X & Y Ramp Generators         | 3-30          |

| Ramp Generators               | 3-30          |

| Scan Amplifiers               | 3-33          |

| Scan Control                  | 3-35          |

| Read Gun Supplies             | 3-35          |

| Cathode Regulator             | 3-36          |

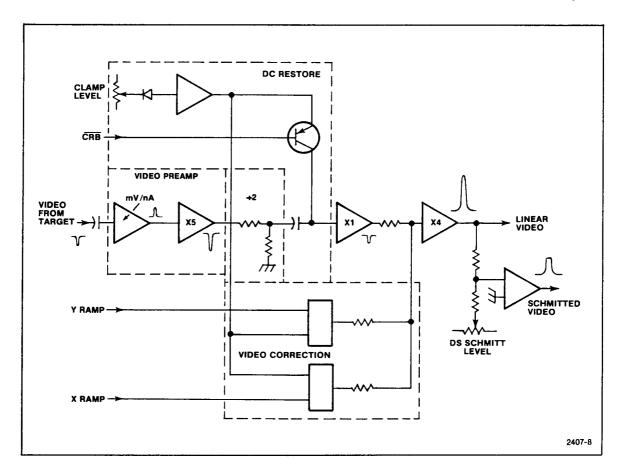

| Video Preamp                  | 3-37          |

| Video Processor               | 3–37          |

| Clamp                         | 3-38          |

| Video Correction              | 3-39          |

| Schmitted Video               | 3-40          |

| Video Outputs                 | 3-41          |

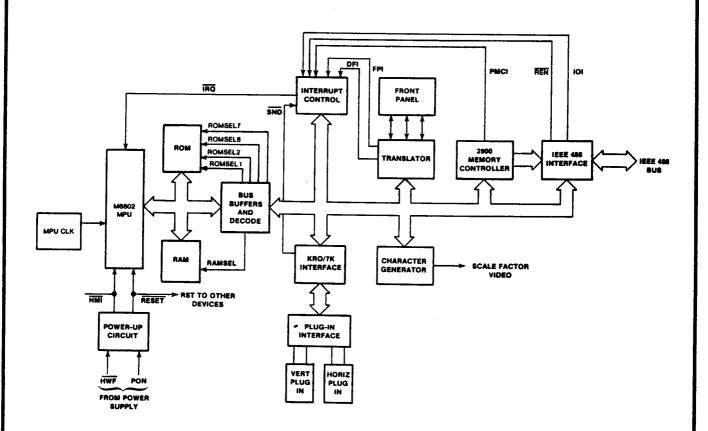

| 6800 Microprocessor System    | 3-42          |

| Block Diagram                 | 3-42          |

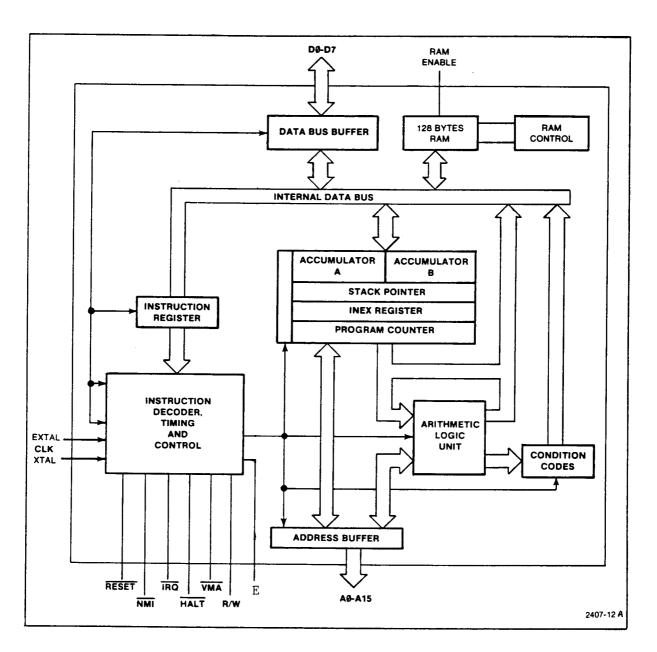

| 6800 MPU Architecture         | 3-44          |

| Accumulators                  | 3-44          |

| Condition Code Register       | 3-44          |

| Program Counter               | 3-44          |

| Stack Pointer                 | 3-45          |

| Index Register                | 3-46          |

| Instruction Register and      | 3-46          |

| Decoder/Timing                |               |

| Data and Address Buffers      | 3-46          |

| The Instruction Cycle         | 3-46          |

| MPU Control Signals           | 3-46          |

| Clock Phase One and Phase Two | 3-46          |

| HALT                          | 3-46          |

| Three-State Control                        | 3-46          |

|--------------------------------------------|---------------|

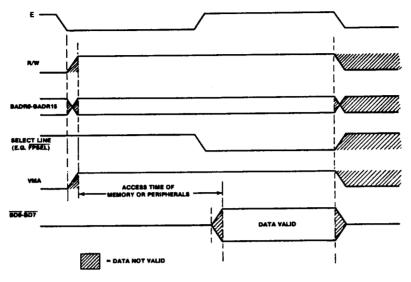

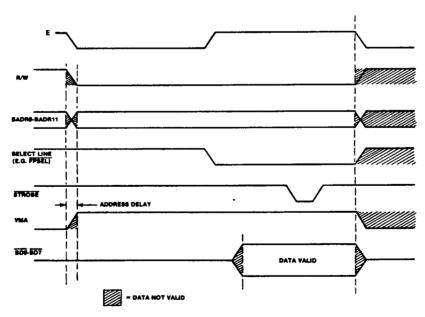

| Read/Write                                 | 3-47          |

| Valid Memory Address                       | 3-47          |

| Data Bus Enable                            | 3-47          |

| Interrupt Request                          | 3-47          |

| Non-Maskable Interrupt                     | 3-49          |

| RESET                                      | 3-49          |

| The 6800 Bus                               | 3-51          |

| Bus Buffers                                | 3 <b>-</b> 53 |

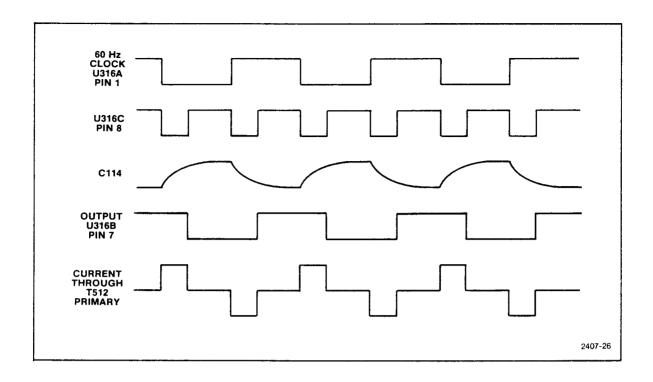

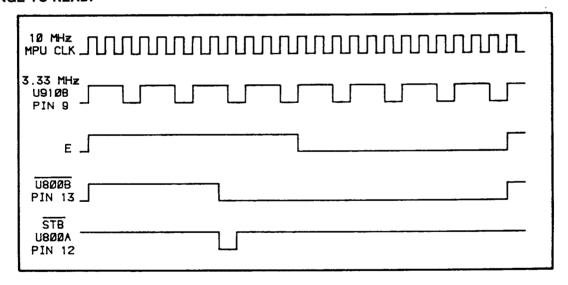

| MPU Clock Circuit                          | 3-53          |

| Reset Circuit                              | 3-55          |

| Power Fail and Hardware Failure Interrupts | 3-55          |

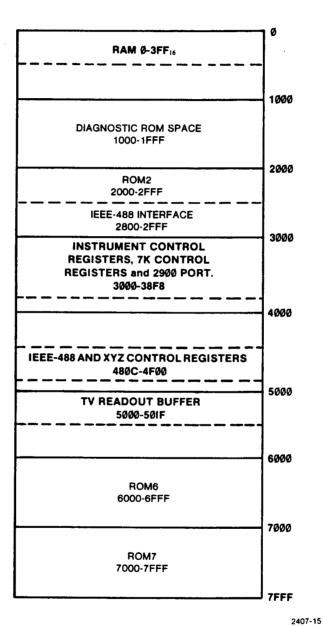

| MPU Memory                                 | 3 <b>-</b> 56 |

| RAM Memory                                 | 3-56          |

| ROM Memory                                 | 3-56          |

| Interrupt Control Logic                    | 3-56          |

| Interrupt Occurred Registers               | 3 <b>-</b> 57 |

| Interrupt Mask Registers                   | 3–58          |

| Readout System Block Diagram               | 3-59          |

| Introduction to the Scale Factor           | 3-59          |

| Readout System                             |               |

| Display Format                             | 3-61          |

| The 7000-Series Readout System             | 3 <b>-</b> 62 |

| Readout Acquisition                        | 3-65          |

| Readout Control Register                   | 3 <b>-</b> 65 |

| Time-Slot Generator                        | 3-66          |

| Analog Data Multiplexer                    | 3 <b>–</b> 68 |

| Analog Data Decoder                        | 3 <b>-</b> 70 |

| Character Generator                        | 3-71          |

| Generating a Raster-Scan Display           | 3-71          |

| Character Generator Block Diagram          | 3 <b>-</b> 73 |

| Dot Clock                                  | 3-74          |

| Column Address Counters                    | 3-74          |

| Row Address Counters       |                 | 3 <b>-</b> 75 |

|----------------------------|-----------------|---------------|

| Memory Select Logic        |                 | 3 <b>-</b> 75 |

| Loading the Character      | Generator       | 3-77          |

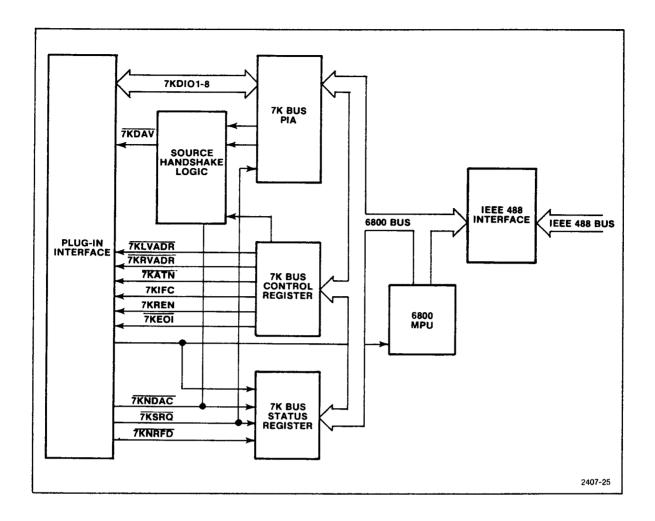

| 7K/IEEE 488 Interface      |                 | 3 <b>-</b> 78 |

| The 7K Bus                 |                 | 3-79          |

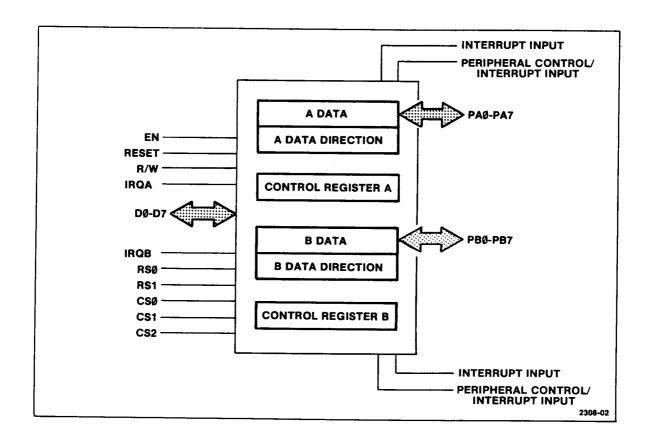

| Peripheral Interface       | Adapters        | 3 <b>–</b> 82 |

| 7K Bus PIA                 |                 | 3 <b>-</b> 82 |

| 7K Bus Control Regist      | er              | 3-84          |

| 7K Bus Status Registe      | r               | 3-85          |

| IEEE 488 Interface Control |                 | 3-86          |

| Introduction               |                 | 3-86          |

| IEEE 488 PIA               |                 | 3-86          |

| IEEE 488 Bus Status R      | egister         | 3 <b>-</b> 89 |

| Talk/Listen Address R      | egister         | 3 <b>-</b> 90 |

| Base Secondary Addres      | s Register      | 3 <b>-</b> 90 |

| Address Decoding, Bus      | Drivers and ROM | 3 <b>-</b> 91 |

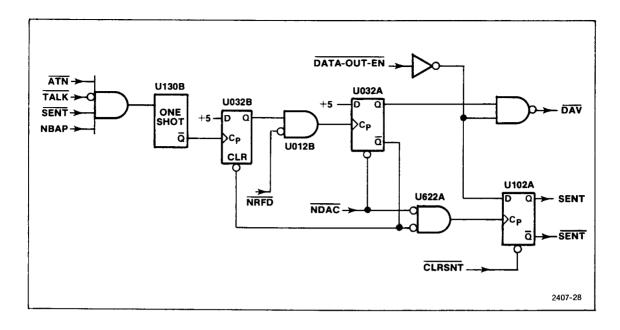

| IEEE 488 Interface Handsha | ke              | 3-92          |

| Source Handshake           |                 | 3 <b>-</b> 92 |

| Acceptor Handshake         |                 | 3 <b>-</b> 95 |

| Attention Messages         |                 | 3 <b>-</b> 95 |

| Interface Clear Latch      |                 | 3 <b>-</b> 96 |

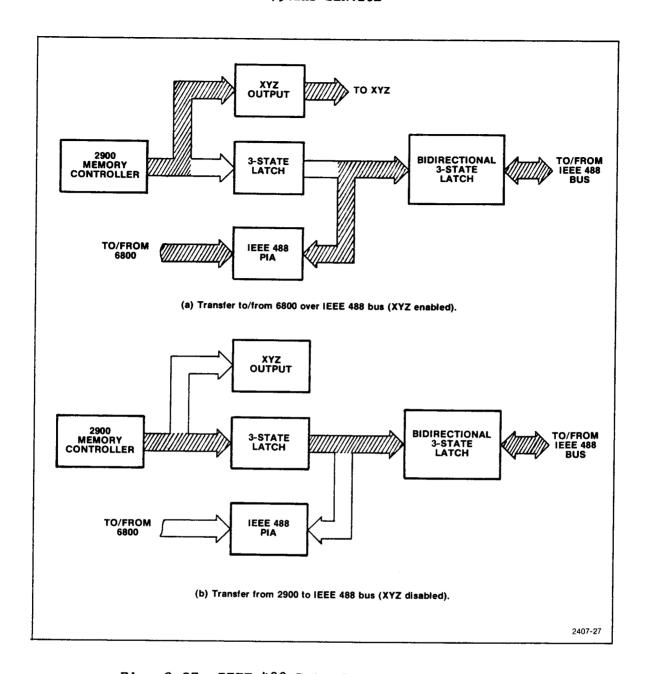

| Memory Controller Tra      | nsfers          | 3 <b>-</b> 96 |

| Translator                 |                 | 3-97          |

| Address Decoding and       |                 | 3-97          |

| Register Select Log        |                 |               |

| Intensity Limit Consta     | ant ROM         | 3-98          |

| Status Register            |                 | 3-98          |

| Action Register            |                 | 3-99          |

| Tracking A/D Converter     |                 | 3-101         |

| Main Intensity Registe     |                 | 3-103         |

| Graticule Intensity Re     | egister         | 3-104         |

| Focus Register             |                 | 3-105         |

| Front Panel Interpret      | - <del>-</del>  | 3-105         |

| Front-Panel Interrupt      | Logic           | 3-106         |

| Duty Factor Register       |                 | 3-107         |

| Duty Factor Generator      |                 | 3-108         |

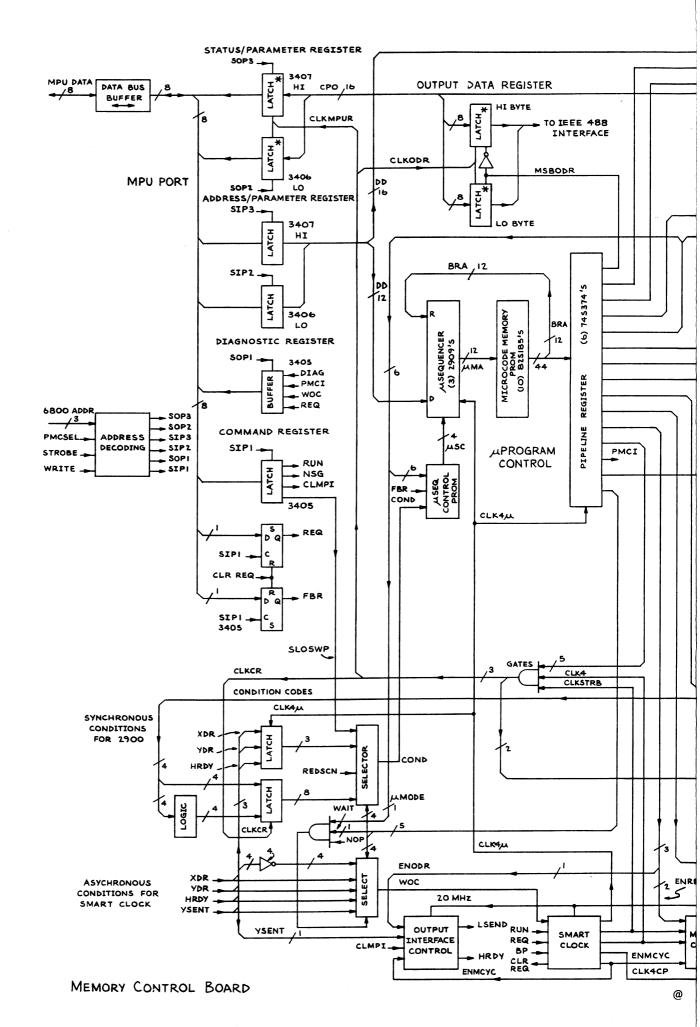

| 2900/MPU Port              | 3-109 |

|----------------------------|-------|

| Command Register           | 3-110 |

| Diagnostic Register        | 3-111 |

| Address/Parameter Register | 3-111 |

| Status/Parameter Register  | 3-111 |

| Address Decoding Logic     | 3–112 |

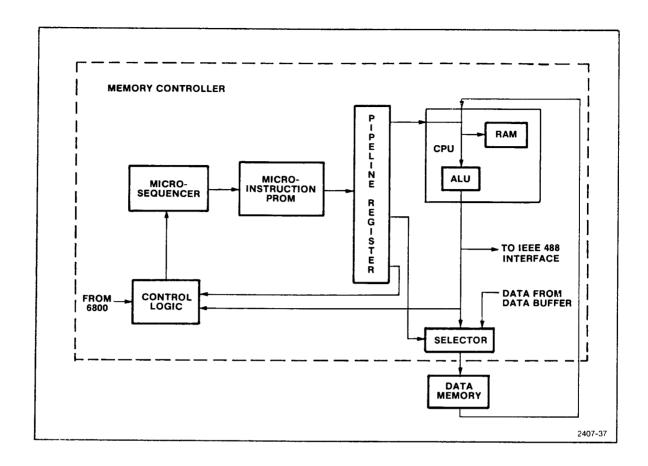

| The 2900 Memory Controller | 3-112 |

| Anatomy of a Computer      | 3-113 |

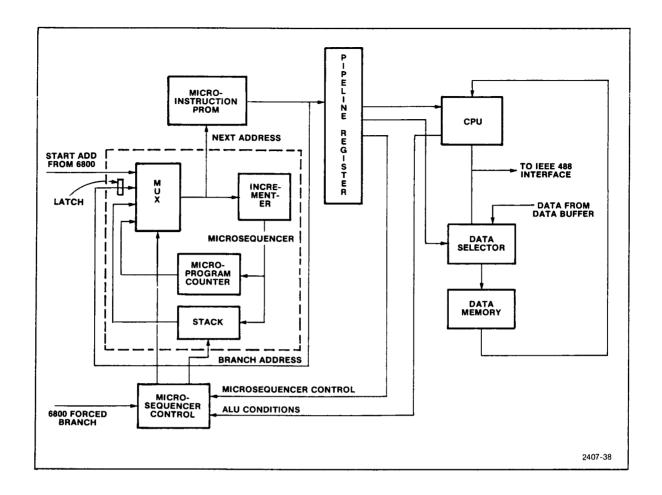

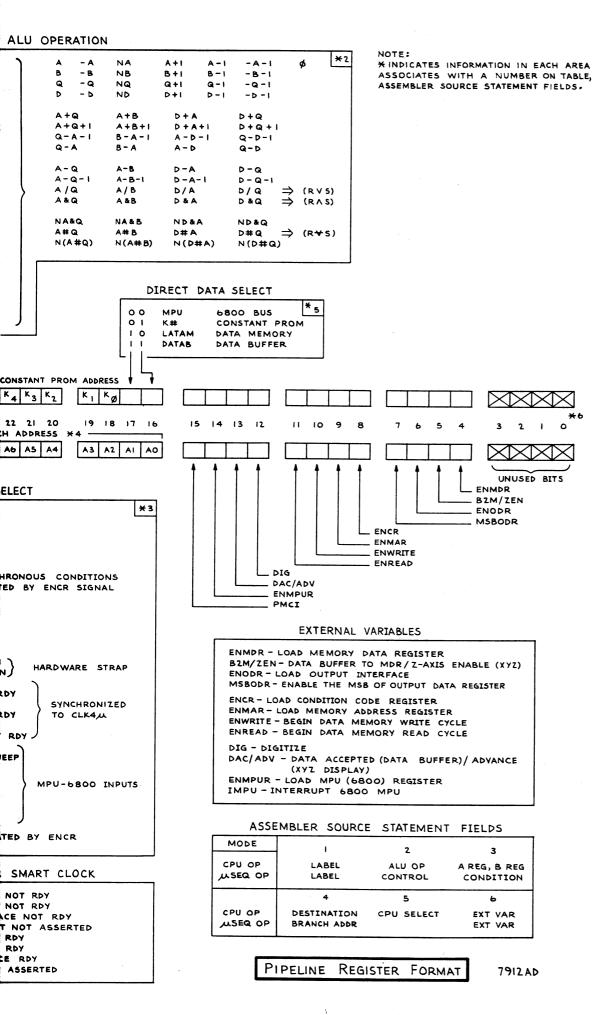

| The Microsequencer         | 3–118 |

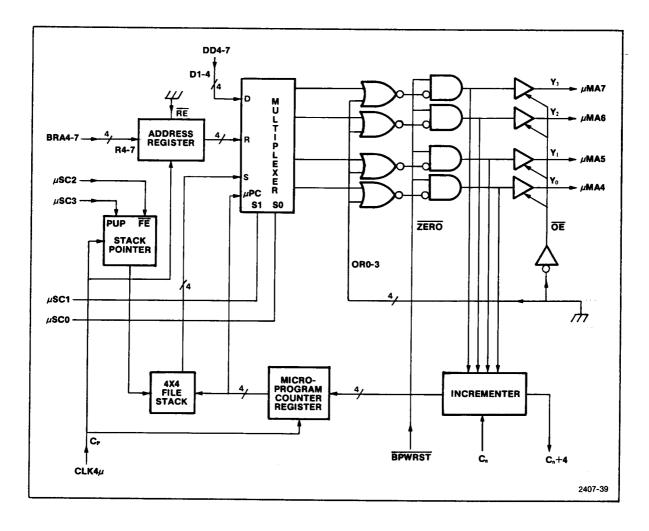

| The 2909                   | 3-119 |

| Microsequencer Control     | 3-121 |

| Synchronous Conditions     | 3-122 |

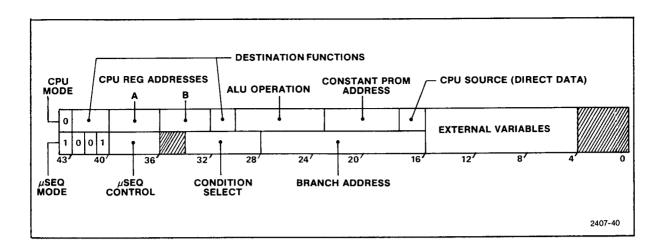

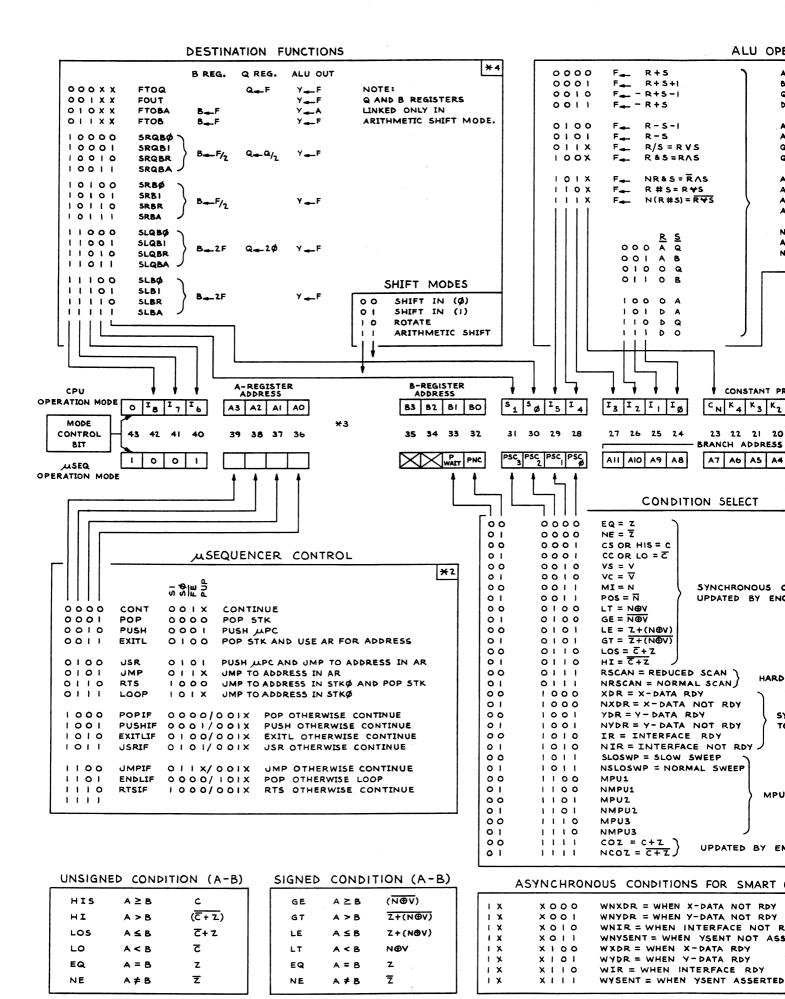

| The Microinstruction Word  | 3–123 |

| Pipeline Register          | 3–123 |

| Microinstruction Format    | 3-124 |

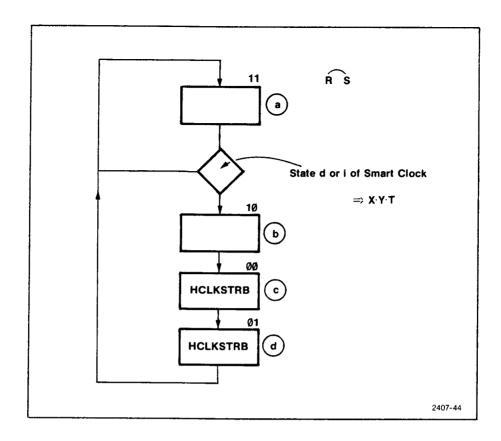

| The Smart Clock            | 3-124 |

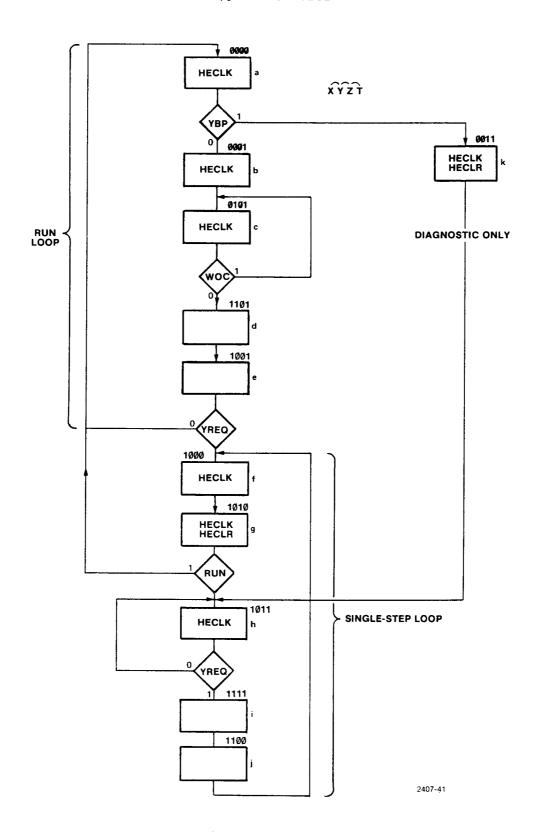

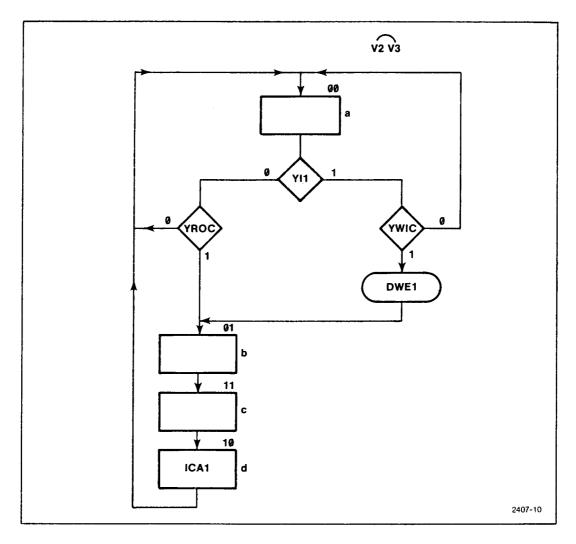

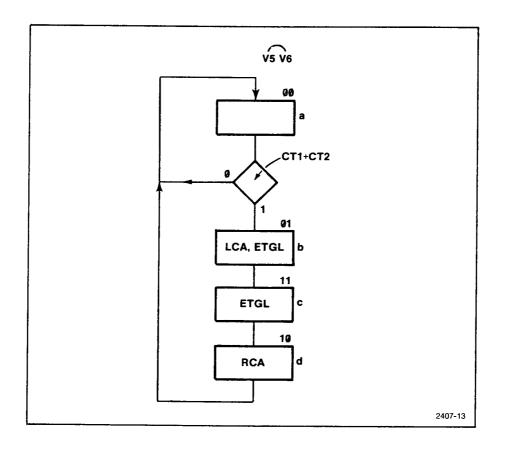

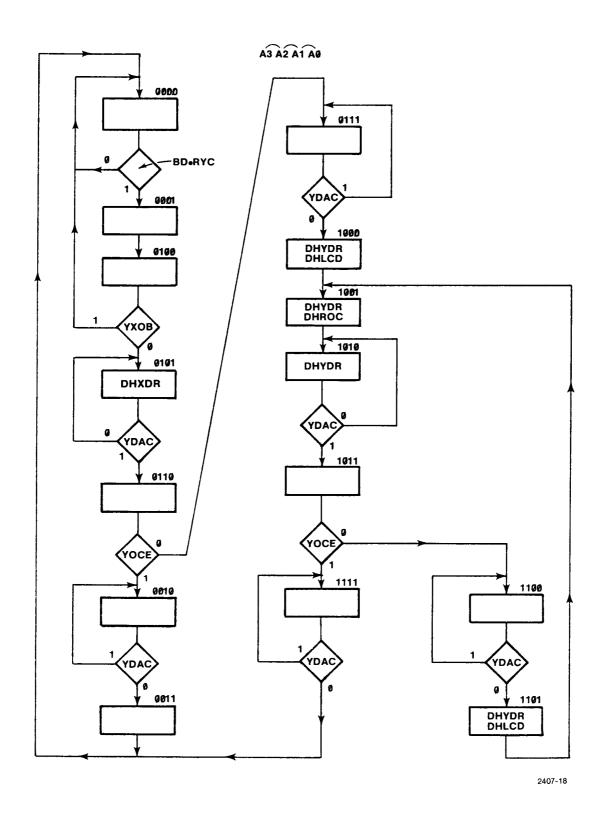

| The State diagram          | 3-126 |

| Asynchronous Conditions    | 3-129 |

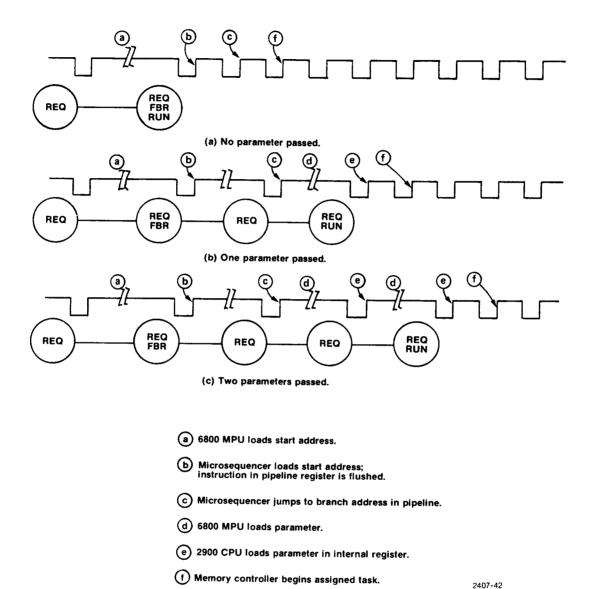

| Stop and Go FBR            | 3-129 |

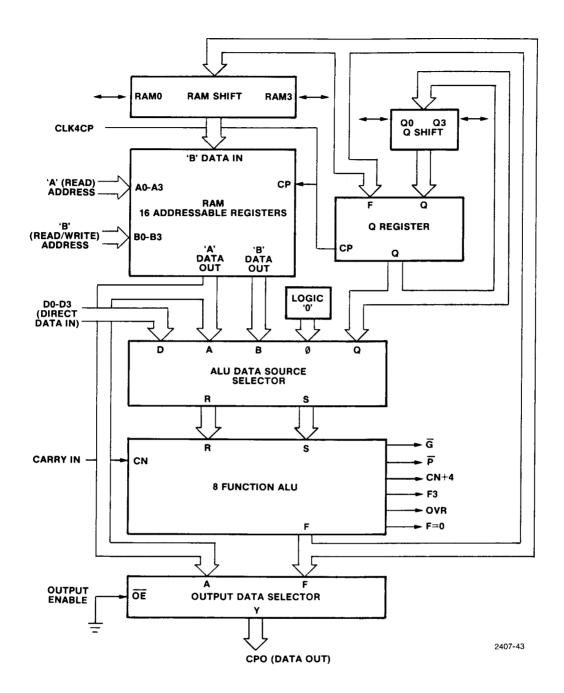

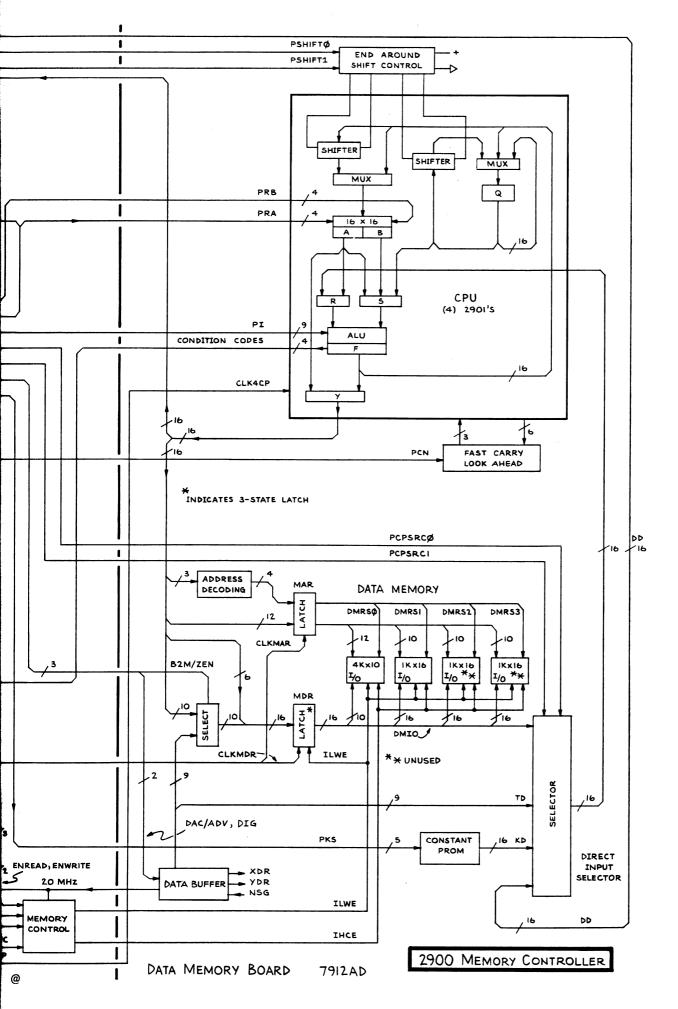

| The 2900 CPU               | 3-130 |

| ALU Data Sources           | 3-132 |

| ALU Outputs                | 3-134 |

| Status Flags               | 3–135 |

| Memory Controller I/O      | 3-136 |

| 6800 MPU I/O               | 3-136 |

| Data Memory Transfers      | 3-137 |

| IEEE 488 Bus Output        | 3-141 |

| XYZ Display Output         | 3-145 |

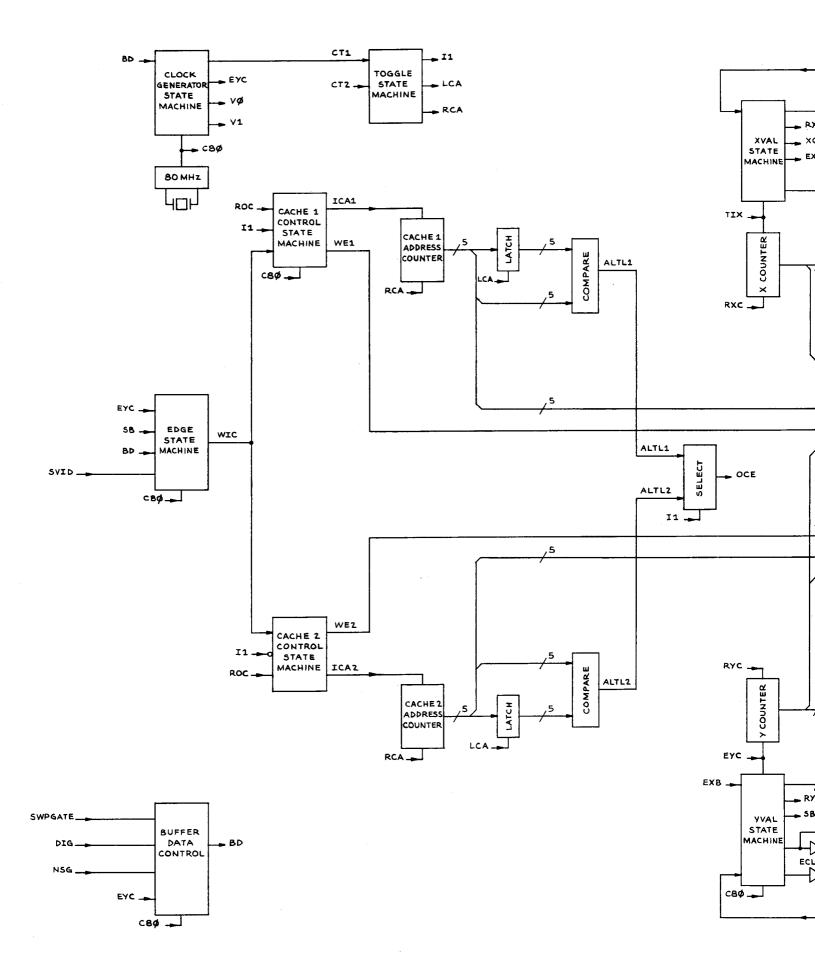

| CTOCKS            |                   | 3-148 |

|-------------------|-------------------|-------|

| 80 MHz Clock      | :                 | 3-148 |

| Clock Genera      | tor State Machine | 3-148 |

| Clock Divide      | er                | 3-149 |

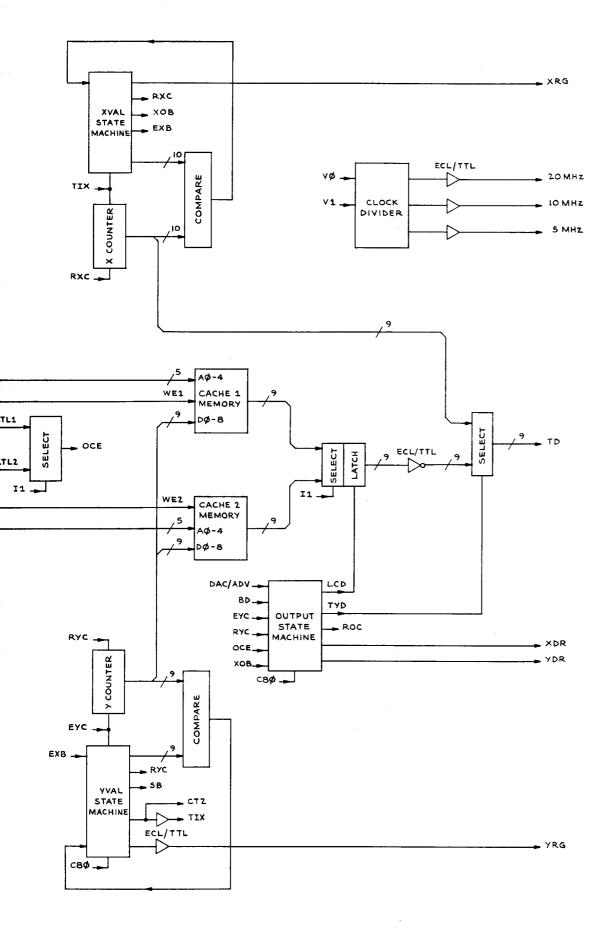

| Ramp Control      |                   | 3-149 |

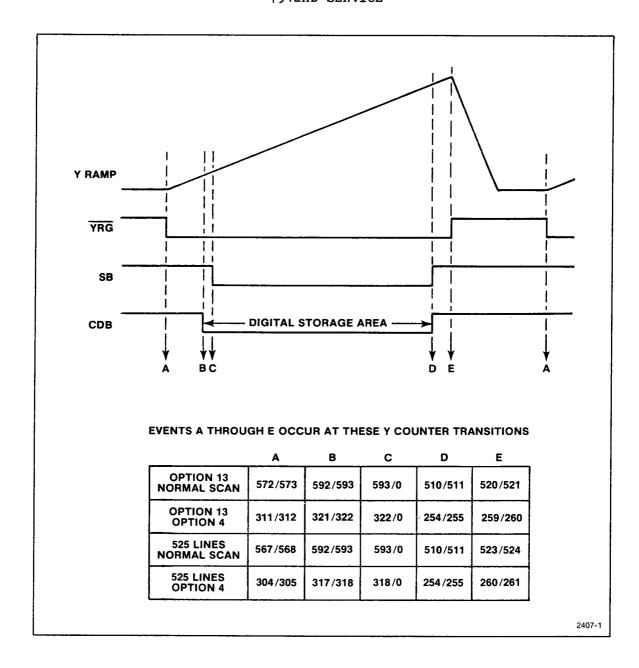

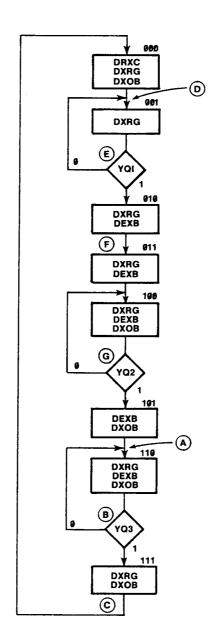

| YVAL State M      | Machine           | 3-150 |

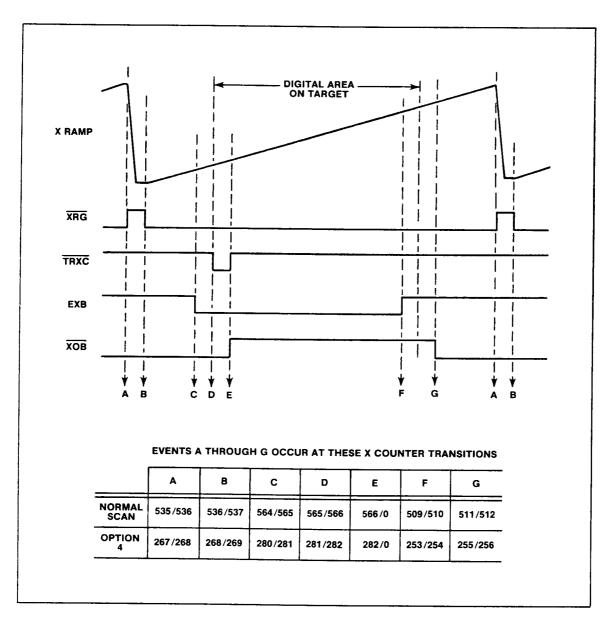

| XVAL State M      | achine (          | 3–156 |

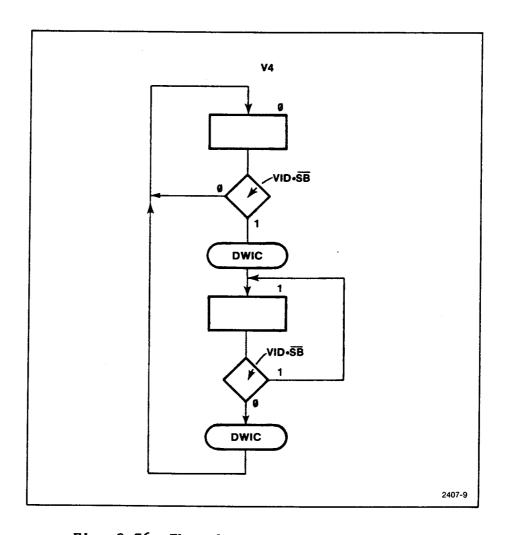

| Data Buffering    |                   | 3-160 |

| Edge State M      | Machine (achine   | 3-161 |

| Cache Contro      | l State Machines  | 3-163 |

| Toggle State      | Machine           | 3-164 |

| Buffer Memor      | у                 | 3-166 |

| Output State      | Machine           | 3–166 |

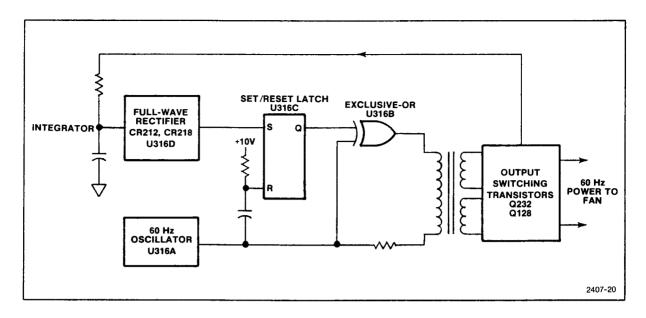

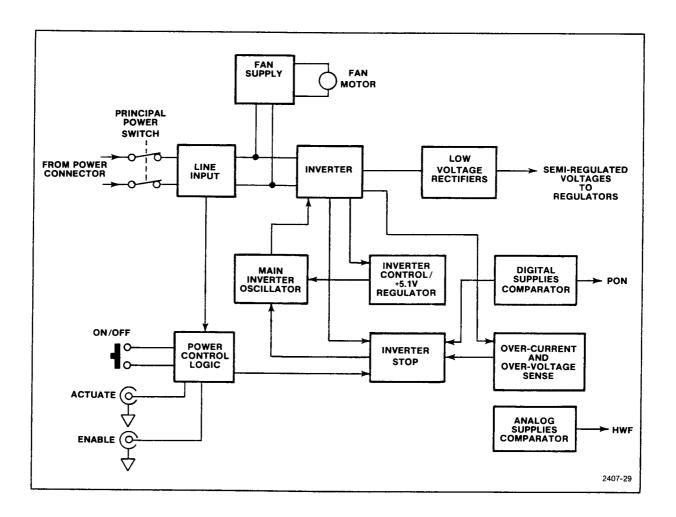

| Power Supply      |                   | 3-170 |

| Introduction      |                   | 3-170 |

| Power Control and | Fan Supply        | 3-170 |

| Line Input        |                   | 3-170 |

| Power Contro      | 1                 | 3-171 |

| Fan Supply        |                   | 3-171 |

| Inverter/Rectifie | r                 | 3-174 |

| Block Diagra      | m                 | 3-174 |

| Main Inverte      | r Oscillator      | 3-174 |

| +5 Volt Refe      | rence             | 3-175 |

| Main Inverte      | r                 | 3-175 |

| Inverter Con      | trol              | 3-175 |

| Over-Current      | Protection        | 3-176 |

| Over-Voltage      | Protection        | 3-176 |

| Digital Supp      | lies Comparator   | 3-177 |

| Low-Voltage Regulators        | 3-177 |

|-------------------------------|-------|

| Overview                      | 3-177 |

| -50 Volt Regulator            | 3-177 |

| -15,+15,+5, and               | 3-178 |

| +50 Volt Regulators           |       |

| +130 and +365 Volt Regulators | 3-179 |

| -5.2 and -2 Volt Regulators   | 3-179 |

| Analog Supplies Comparator    | 3-180 |

| Power Distribution            | 3-181 |

### VOL. II

### SAFETY SUMMARY

### PREFACE

SECTION 4 - INSTALLATION AND MAINTENANCE

SECTION 5 - CALIBRATION

SECTION 6 - REPLACEABLE ELECTRICAL PARTS LIST

SECTION 7 - DIAGRAMS

SECTION 8 - REPLACEABLE MECHANICAL PARTS LIST

### SAFETY SUMMARY

This manual contains safety information which the user must follow to ensure safe operation of the instrument. The following safety information and precautions must be observed during all phases of operation and maintenance.

### Terms and Symbols

WARNING statements identify conditions or practices that could result in damage to the equipment or property.

CAUTION statements identify conditions or practices that could result in damage to the equipment or other property.

DANGER, as it appears on equipment, identifies areas of immediate hazard that could result in personal injury or loss of life.

Protective ground (earth) terminal.

### Power Source

The 7912AD is entended to operate from a power source that does not apply more than 250 volts rms between the supply conductors or between either supply conductor and ground. A protective-ground connection by way of the grounding conductor in the power cord is essential for safe operation.

### Ground the Instrument

The 7912AD is grounded through the grounding conductor of the power cord. To avoid electric shock, plug the power cord into a properly wired receptacle before connecting to 7912AD inputs or outputs.

### Use the Proper Power Cord

Use only the power cord and connector specified in the parts list. Use only a power cord that is in good condition.

### Use the Proper Fuse

To avoid fire hazard, use only the fuse that is specified in the parts list for your instrument and that is identical in type, voltage rating, and current rating.

### Do Not Operate in an Explosive Atmosphere

To avoid explosion, do not operate this instrument in an atmosphere of explosive gases unless it has been specifically certified for such operation.

### Do Not Service Alone

Do not perform internal service or adjustment of this instrument unless another person capable of rendering first aid and resuscitation is present.

### Use Care When Servicing With Power On

Dangerous voltages exist at several points in this instrument. To avoid personal injury, do not touch exposed connections and components while power is on.

Disconnect power before removing protective panels, soldering, or replacing components.

### PREFACE

This service manual is provided to assist in the service and repair of the 7912AD Programmable Digitizer. It is intended for qualified service personnel only.

Volume I contains an introduction to the 7912AD and operating and programming information to help the service person understand and operate the instrument. A block diagram and detailed circuit description follow.

Volume II contains maintenance information and a calibration procedure. At the rear are electrical and mechanical parts lists and electrical and mechanical diagrams.

For more operating and programming information, see the 7912AD Operators Manual. For a full discussion of the IEEE 488 bus to which this instrument can be interfaced, see IEEE Standard 488-1975, the IEEE Standard Digital Interface for Programmable Instrumentation.

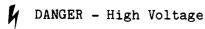

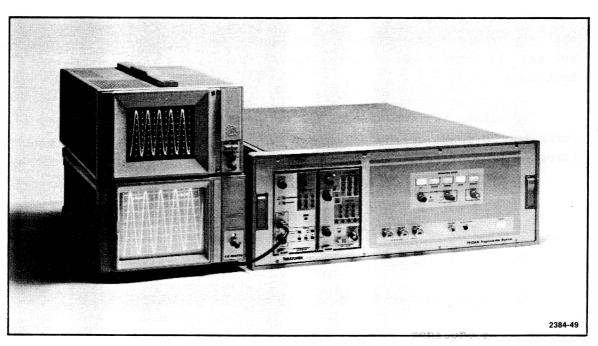

The 7912AD Programmable Digitizer with programmable plug-ins.

### SECTION 1

### INTRODUCTION

The TEKTRONIX 7912AD Programmable Digitizer is a wide-bandwidth waveform acquisition instrument with both analog and digital outputs. Programming is accomplished over the bus specified in IEEE Standard 488-1975.

Two operating modes are provided. In the digital mode, the 7912AD digitizes either a single-shot or repetitive waveform and stores it for internal processing or for output on the IEEE 488 bus. Analog outputs are also provided to display the waveform data on an X-Y-Z monitor. In the TV mode, the 7912AD converts a waveform to a composite video output. This allows the input waveform to be displayed on a TV monitor such as the TEKTRONIX 634 Monitor, one of the 650- and 670-series of color Picture Monitors.

In either the TV or digital mode, the 7912AD can acquire waveforms with high bandwidths: up to 500 MHz with the TEKTRONIX 7A19 Amplifier plug-in, for instance, or 1 GHz with the TEKTRONIX 7A21N Direct Access plug-in. The time window can be selected between 10 milliseconds and 5 nanoseconds using a TEKTRONIX 7000-series time base plug-in. This is equivalent to sampling rates (in digital mode) from 50 kHz to 100 GHz.

Remote control and data output via the IEEE 488 bus is simplified by two microprocessor systems in the 7912AD. The firmware operating systems for these microprocessors is designed to let the programmer talk to the 7912AD in as simple and obvious a manner as possible.

Design of the firmware that controls the IEEE 488 interface is consistent with the IEEE 488-1975 standard. Extended addresses are used so that the 7912AD can act as a transparent interface for programmable plug-ins (if installed). These plug-ins include the 7A16P Programmable Amplifier and the 7B90P Programmable Time Base.

The 7912AD operates in many respects like an oscilloscope such as those in the TEKTRONIX 7000-series. The input signal is connected to a vertical plug-in to drive the vertical deflection amplifer. A number of 7000-series plug-ins are available to tailor the 7912AD for bandwidth, input impedance, differential or single-ended input, and input voltage. On most vertical plug-ins, a wide range of deflection factors

(amplification) can be selected on the front panel. A number of 7000-series time base plug-ins are available to drive the horizontal deflection amplifier at calibrated sweep rates.

Although the vertical and horizontal deflection systems of the 7912AD are similar to those of an oscilloscope, the similarity ends there. In place of the oscilloscope CRT, there is a scan converter tube. Instead of displaying the input waveform as a trace on the phosphorcoated face of a CRT, the input waveform is written on a silicon diode matrix and read from this target as in a vidicon TV camera.

### The Scan Converter

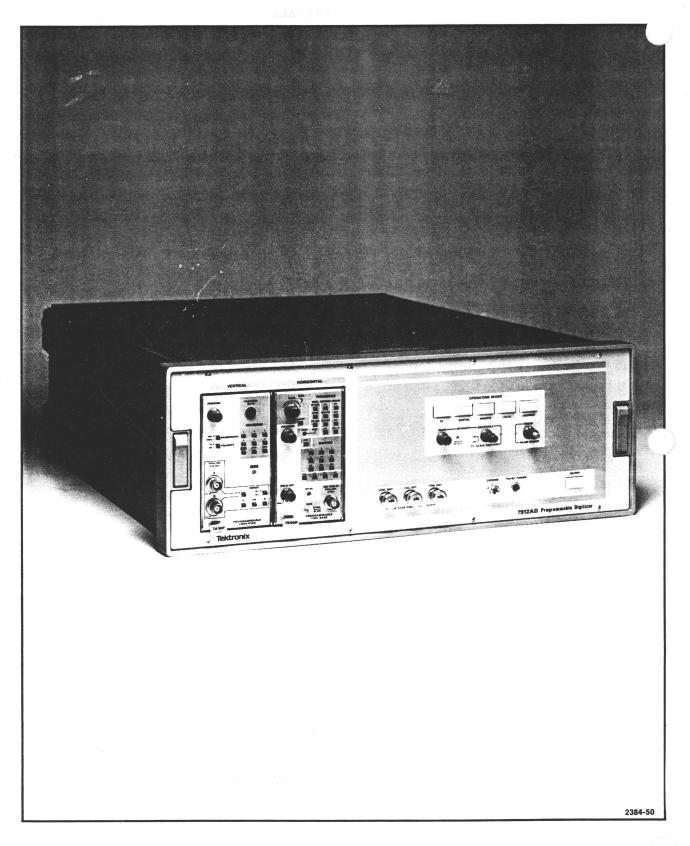

Because of the high writing rate of the scan converter, the 7912AD performs at high bandwidths and sampling rates not usually obtained with other digitizing techniques. The high writing rate stems from several factors that can be understood only by considering the design of the scan converter. The scan converter is an electron tube with dual electron guns, one at each end of the tube. Between the two guns is the target (Fig. 1-1).

Fig. 1-1. The 7912AD scan converter tube.

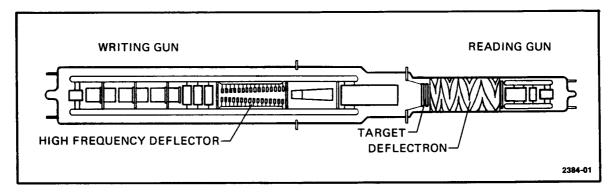

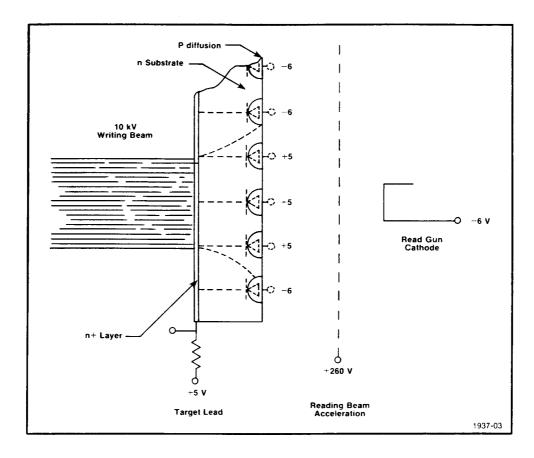

The target is an array of diodes formed on an n-type silicon wafer by integrated circuit techniques (Fig. 1-2). In operation, the target substrate is held positive with respect to the reading gun cathode by the target lead. The target is scanned continuously by the reading beam, charging each diode toward the more negative cathode potential to reverse-bias it.

When the time base is triggered, it unblanks the writing gun and applies a ramp to the horizontal deflection plates of the writing gun to write a trace across the target. At the same time, the input signal is

Fig. 1-2. The 7912AD scan converter target. The area scanned is approximately 1.3 X 0.95 centimeters with a diode density of about 800 per centimeter.

applied to the vertical deflection plates to vary the height of the trace according to the amplitude of the input signal.

The writing gun electrons, accelerated by the 10-kilovolt potential between the gun and target, bombard the target (Fig. 1-3). Each electron creates many electron-hole pairs near the surface. The holes diffuse through the target and drift across the depletion region at the p-n junction, causing the adjacent diodes to conduct and discharge. When the reading beam next scans the target, little or no current flows at points that were not written. Where the target was written, however, the diodes are recharged and a signal current can be detected in the target lead. This output signal is amplified for further processing.

Fig. 1-3. The scan converter tube in operation showing the effect of the reading beam.

Since the energy required to create an electron-hole pair in silicon is about 3.6 electron volts, roughly 2,780 electron-hole pairs are created by each 10-kV electron that strikes the target. Accounting for certain losses, the effective charge gain in the target is about 2,000. This gain is responsible for the high-speed performance of the scan converter because few electrons need to strike the target to record a waveform, allowing the writing trace to be deflected at high speeds.

Other advantages stem from writing and reading the waveform on the target. Because the target is small, the writing beam need only be deflected over a small area (about 1.3 X 0.95 centimeters). Only the writing beam need be high-velocity; the reading beam can be scanned more slowly.

### TV Mode

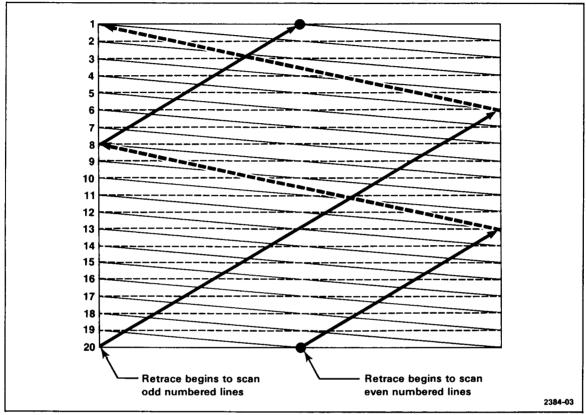

In TV mode, the target is scanned horizontally by the reading beam in a conventional television format with a 525-line (625-lines with option 13) raster. This scan mode is shown in Fig. 1-4. The output signal is amplified, a sync waveform is added, and the composite video signal is provided to two output connectors on the 7912AD rear panel.

Fig. 1-4. A small-scale example of an interlaced horizontal scan such as is used in the 7912AD TV mode.

One output, LINEAR, is a replica of the output of the target lead. The signal goes positive (white) whenever the reading beam crosses a portion of the target that is written; its amplitude varies with the intensity with which that portion of the target was written.

The other output, BINARY, is a two-level output derived from the LINEAR signal. A comparator sets the video level high when it detects that the writing beam crosses a portion of the target that is written. The comparator sets the video level low at all other times during the scan.

To provide the waveform scale factors as part of the monitor display, a character generator adds the readout from the plug-ins to the composite video outputs.

The TV mode provides several advantages over a conventional oscilloscope display. The monitor can be larger and it can be located some distance from the 7912AD. The TV monitor can be used to set up the 7912AD and plug-in controls for data acquisition. The effect of the intensity controls can be observed, for instance. If the BINARY output is used, the output of the comparators can be displayed to assure that all parts of the waveform will be digitized in the digital mode at a particular intensity setting.

### Digital Mode

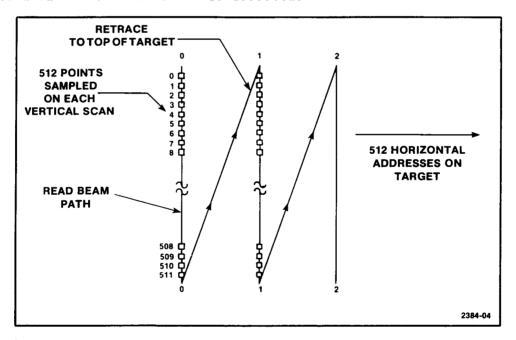

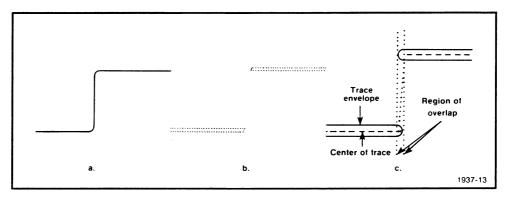

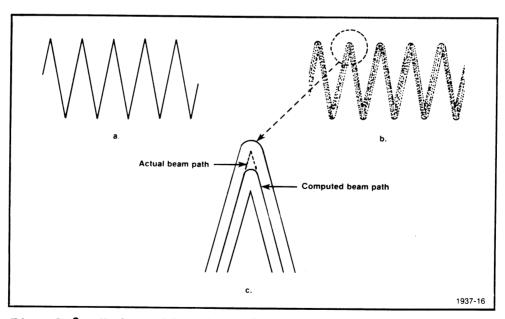

In the digital mode, the target is scanned vertically by the reading beam in a 512 X 512 point format (Fig. 1-5). The signal from the target lead is amplified and fed to a comparator. If the signal is above the comparator threshold, the comparator switches to a high state to indicate that the reading beam is crossing a portion of the target that is written. If the signal is below the threshold, the comparator switches low to indicate that no trace is detected.

Fig. 1-5. In digital mode, the target is scanned along 512 vertical lines from left to right.

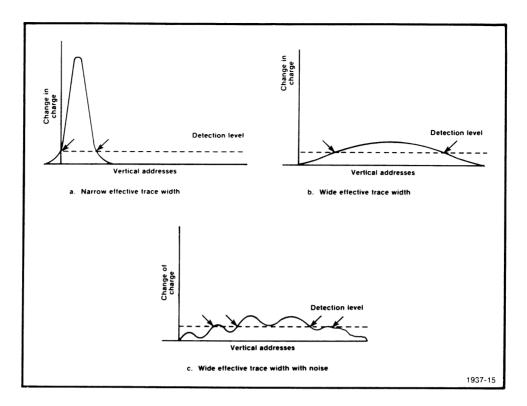

The 7912AD begins to store data on the next time base trigger after either the DIGITAL button is pressed (local mode) or a digitize command is received (remote mode). Two counters are the source of the data. One counter is incremented from 0 to 511 as the reading sweeps down the target. Each time the counter is incremented, the output of the

comparator is sampled. If the comparator has changed state since the last sample, the count is complemented and stored in memory in the Y (vertical) array.

As a result, two data values are usually stored during each vertical scan, one for the top of the trace and one for the bottom of the trace. Data are always stored in pairs. If the top of a written portion of the target is detected, the bottom will be detected as well. Up to 30 data can be stored to handle graticule and dual traces. The data are complemented so 511 corresponds to the top of the target and zero to the bottom.

Meanwhile, another counter is incremented each time the reading beam begins another vertical scan. The value of the counter is used to address a location in an X (horizontal) array where the number of data points detected by that vertical scan is stored. When read, the X and Y arrays are used by 7912AD microprocessor routines or external data processing to recover the X and Y coordinates of all points detected as data on the target.

### **Options**

The following options are available for the 7912AD. They are not field-installable; instructions are not provided in the 7912AD manuals to modify the 7912AD for these options. Changes to the replaceable parts lists are detailed in the service manual for the 7912AD.

**Option 4.** Change to fast digitize mode. The scan time to read a waveform from the target and into local memory is reduced by compressing the scan. The target is written on and read from a 256 X 256 point matrix with a maximum of 14 points stored per vertical scan. However, the data are normalized to a 512 by 512 point matrix before further processing or output. Vertical values are multiplied by two and the data are blown up to 512 points horizontally by treating every other point as if it is empty.

Graticule resolution is cut by one-half; every other major division is marked in digital mode, and every other major and minor division is marked in TV mode. Both the TV and XYZ displays are restored to the same size as the non-option 4 displays.

This option changes the minimum sweep rate to 200 microseconds/division. This is the lower limit on sweep rate for digitizing reliable data in fast-digitize mode.

Option 9. Set instrument for 230 VAC operation; substitute a 230 volt power cord.

**Option 13.** Change TV scan rate. The TV mode reading scan of the target is changed to 625 lines per frame with a 50 hertz field rate. The composite video outputs, sync input, and sync output are changed to match this scan rate.

**Option 30.** Delete cable. The IEEE 488 bus cable that is a standard accessory is deleted.

### **Specifications**

Electrical characteristics of the 7912AD are listed in Table 1-1, Table 1-2, and Table 1-3. To be valid, the following conditions apply:

- 1) The 7912AD and plug-ins must be calibrated at an ambient temperature between +20 and +30 degrees C.

- 2) The 7912AD and plug-ins must be allowed to warm up for at least 20 minutes with all covers installed.

- 3) The calibration of the 7912AD must be checked according to the calibration procedure within each 1000 hours of operation or every six months if operated infrequently. Any adjustments that cause performance outside the limits allowed by the calibration procedure must be readjusted. The plug-ins must also be operated within their calibration intervals.

- 4) The 7912AD and plug-ins must be operated within their specified environmental limits (Table 1-4). In some cases, an electrical characteristic applies only to a limited temperature range or must be derated to apply to the entire temperature range. These cases are noted.

Statements in the Performance Requirements column are verified by the steps marked with a in the calibration procedure, Section 5 (Vol. II). Statements listed in the Supplemental Information column are not verified in the calibration procedure and are not to be construed as performance requirements of the 7912AD.

Physical characteristics are listed in Table 1-5.

TABLE 1-1

# ELECTRICAL SPECIFICATIONS

| Characteristics                | Performance<br>Requirements                                                                                                                                                                 | Supplemental<br>Information                                                                |

|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|

|                                | VERTICAL DEFLECTION SYSTEM                                                                                                                                                                  |                                                                                            |

| Deflection factor              | Compatible with all 7000-Series amplifier plug-in units.                                                                                                                                    | Full-scale deflection is $\pm^4$ divisions.                                                |

| Relative accuracy              | See Table 1-2.                                                                                                                                                                              |                                                                                            |

| Centering                      | Zero-volt input can be centered by plug-in position control.                                                                                                                                | Within 0.5 division of electronic graticule center with no plug-in (1 division, option 4). |

| Low-frequency<br>linearity     | 0.1 division or less compression or expansion of a centered, two-division waveform. This limit is not exceeded if the waveform is positioned anywhere within the electronic graticule area. |                                                                                            |

| Bandwidth                      | See Table 1-2.                                                                                                                                                                              |                                                                                            |

| Rise time                      | See Table 1-2.                                                                                                                                                                              |                                                                                            |

| Isolation, signal to graticule | At least 100:1 up<br>to 250 MHz; at least<br>40:1 from 250 MHz<br>to 500 MHz.                                                                                                               |                                                                                            |

TABLE 1-1 (cont.)

| Characteristics        | Performance<br>Requirements                                                                                                                 | Supplemental<br>Information                                                                                                          |

|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|

| Delay line             | Adds approximately 60- nanosecond delay in vertical signal path to permit view- ing or digitizing of leading edge of trig- gering waveform. |                                                                                                                                      |

| 19-1-48-1              | GRATICULE                                                                                                                                   | <u> </u>                                                                                                                             |

| Format                 | 8 vertical divisions X 10 horizontal divisions.                                                                                             |                                                                                                                                      |

| TV mode                | Both major and minor divisions marked, five minor divisions per major division.                                                             |                                                                                                                                      |

| Digital mode           | Only major divisions marked.                                                                                                                |                                                                                                                                      |

| TV mode,<br>option 4   | Only every other major and minor division marked.                                                                                           |                                                                                                                                      |

| Digital mode, option 4 | Only every other major division marked.                                                                                                     |                                                                                                                                      |

| Writing time           |                                                                                                                                             | Requires 3 milli- seconds, gated imme- diately after wavefor is acquired. Locks ou vertical signal and main sweep and disabl Z-axis. |

TABLE 1-1 (cont.)

| Characteristics    | Performance<br>Requirements                                                           | Supplemental<br>Information                 |

|--------------------|---------------------------------------------------------------------------------------|---------------------------------------------|

| Position           |                                                                                       | Adjustable horizontally and vertically ±5%. |

| Amplitude          |                                                                                       | Adjustable horizontally and vertically ±5%. |

| Intensity          | Controlled from front panel or by program-med command separately from main intensity. |                                             |

| Stability          |                                                                                       |                                             |

| 0 to +40 degrees C |                                                                                       | 0.5%.                                       |

| +20 to +30 deg. C  | ·                                                                                     | 0.1%.                                       |

# HORIZONTAL DEFLECTION SYSTEM

| Deflection factor | Compatible with all 7000-Series plug-in units. See Table 1-3 for recommended time base plug-ins.                                                  | Full scale deflection is ±5 divisions. |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| DC linearity      | 0.05 division or less error at each graticule line after adjusting for no error at the second and tenth graticule lines (0.1 division, option 4). |                                        |

TABLE 1-1 (cont.)

| Characteristics                                                                 | Performance<br>Requirements                                                                                                                                                  | Supplemental Information |

|---------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|

| Fastest calibrated<br>sweep rate (with<br>7B90P, 7B92A, or<br>7B80GB Time Base) | 0.5 nanosecond/division.                                                                                                                                                     |                          |

| Slowest sweep rate                                                              | 1 millisecond/division (200 microseconds/division, option 4).                                                                                                                |                          |

| Centering                                                                       | Center of sweep can<br>be centered in grati-<br>cule by time base<br>Position control.                                                                                       |                          |

| Bandwidth, 10 divi-<br>sion reference                                           | DC to at least 1 megahertz.                                                                                                                                                  |                          |

|                                                                                 | EXTERNAL Z-AXIS INPUT                                                                                                                                                        |                          |

| Polarity                                                                        | Positive-going signal decreases trace intensity of writing gun; negative-going signal increases trace intensity. Zero-volt (approximate) input produces no intensity change. |                          |

| Sensitivity                                                                     | Two volts peak-to-peak provides trace modula-tion over full intensity range.                                                                                                 |                          |

| Low-frequency<br>limit                                                          |                                                                                                                                                                              | DC                       |

TABLE 1-1 (cont.)

| Characteristics       | Performance<br>Requirements | Supplemental Information |

|-----------------------|-----------------------------|--------------------------|

| DC input resistance   |                             | 550 ohms, <u>+</u> 10%.  |

| Maximum Input voltage |                             | 15 volts (DC + peak AC). |

# CRT TARGET AND WRITING GUN

| Gun type      | Monoaccelerator.                                                                                                                       |  |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------|--|

| Light defects |                                                                                                                                        |  |

| Distribution  | No more than six points digitized or displayed other than those written by input waveform. No two light defects on same vertical line. |  |

| Size          | No light defects larger than six TV lines.                                                                                             |  |

| Geometry      | A straight-line input is read from the target as a straight line within 0.1 division.                                                  |  |

TABLE 1-1 (cont.)

| Characteristics                     | Performance<br>Requirements                                                                                                    | Supplemental<br>Information                                                   |

|-------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|

| Writing Rate (+10 to +40 degrees C) |                                                                                                                                |                                                                               |

| TV mode                             | Writes an 8-division sine wave of at least 500 MHz in a single sweep.                                                          | At least 12.5 divisions per nanosecond; 30 divisions per nanosecond, typical. |

| Digital mode                        | Writes a single 8- division pulse with a rise time of 1 nano- second or less (2 nanoseconds or less from 0 to +10 degrees C).  | At least 8 divisions per nanosecond, typical.                                 |

| Option 4                            |                                                                                                                                |                                                                               |

| TV mode                             | Writes an 8-division sine wave of at least 1 GHz in a single sweep.                                                            | At least 25 divisions per nanosecond; 60 divisions per nanosecond, typical.   |

| Digital mode                        | Writes a single 10- division pulse with a risetime of 0.5 nano- second or less (1 nanosecond or less from 0 to +10 degrees C.) | At least 20 divisions per nanosecond, typical.                                |

TABLE 1-1 (cont.)

| Characteristics                    | Performance<br>Requirements | Supplemental<br>Information                                                                                                    |

|------------------------------------|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------|

|                                    | READING GUN                 |                                                                                                                                |

| Type                               | Monoaccelerator             |                                                                                                                                |

|                                    | RAMP GENERATOR AND SCAN     | AMPLIFIER                                                                                                                      |

| Scan time, digital mode            |                             | Approximately 16.4 milliseconds per wave- form to read waveform and store in memory (approximately 4.5 milliseconds, option 4) |

|                                    | VIDEO SYSTEM                |                                                                                                                                |

| Resolution                         |                             |                                                                                                                                |

| TV mode                            |                             | At least 400 TV lines per picture width. Video signal is down less than 50% at linear output.                                  |

| Ultimate<br>resolution,<br>TV mode |                             | At least 500 TV lines when viewed on a TEKTRONIX 632 Monitor or equivalent.                                                    |

TABLE 1-1 (cont.)

| Characteristics | Performance<br>Requirements                                                                                                                                                                                        | Supplemental<br>Information |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|

| Digital mode    |                                                                                                                                                                                                                    |                             |

| Horizontal      | Two signals, each in- cluding a step with a risetime of 10 nanoseconds, are digitized separately at a sweep speed of 50 nanoseconds/division if the steps are delayed 1.25 nanoseconds with respect to each other. | 400 lines.                  |

| Vertical        | A 50 milivolt square wave is resolved at 2 volts/division.                                                                                                                                                         | 320 lines.                  |

|                 | VIDEO OUTPUTS                                                                                                                                                                                                      | 1                           |

| Composite video |                                                                                                                                                                                                                    |                             |

| Linear          | 1 volt into 75 ohms for full white signal. Conforms to EIA RS-170.                                                                                                                                                 |                             |

| Binary          |                                                                                                                                                                                                                    |                             |

| Low level       | 0 to +0.3 volts into 75 ohms.                                                                                                                                                                                      |                             |

| High level      | +1 volt <u>+</u> 0.1 volt into 75 ohms.                                                                                                                                                                            |                             |

| Sync out        | At least +4 volts into 75 of Conforms to EIA RS-170.                                                                                                                                                               | <br>hms.<br>                |

TABLE 1-1 (cont.)

| Characteristics          | Performance<br>Requirements                                                                       | Supplemental<br>Information                     |

|--------------------------|---------------------------------------------------------------------------------------------------|-------------------------------------------------|

| Scan rate                |                                                                                                   |                                                 |

| Standard                 |                                                                                                   | 525 lines/frame, 60 Hz field rate (interlaced). |

| Option 13                |                                                                                                   | 625 lines/frame, 50 Hz field rate (interlaced). |

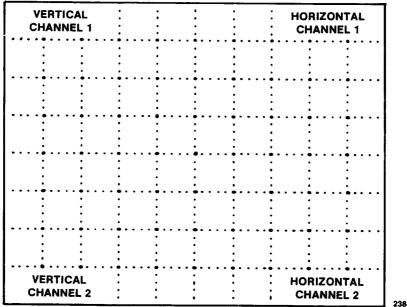

| Scale factor readout     | Up to eight characters per channel.                                                               |                                                 |

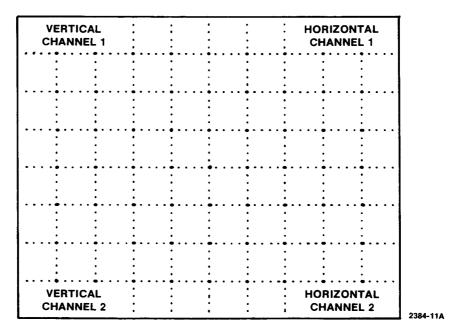

| VERTICAL<br>plug-in      | Channel 1 appears in upper left corner of graticule, channel 2 in lower left corner of graticule. |                                                 |

| HORIZONTAL plug-in       | Channel 1 appears in upper right corner of graticule, channel 2 in lower right corner.            |                                                 |

| Return losses, sync loop |                                                                                                   | At least 40 dB to 4 megahertz.                  |

|                          | IBEE 488 Interface                                                                                | <u> </u>                                        |

| Data connector           | Conforms to IEEE Standard 488-1975.                                                               |                                                 |

| Signal levels            |                                                                                                   | Conform to IEEE Standard 488-1975.              |

| Signal timing            |                                                                                                   | Conforms to IEEE Standard 488-1975.             |

TABLE 1-1 (cont.)

| Characteristics                                     | Performance<br>Requirements                                                                                    | Supplemental<br>Information                                          |

|-----------------------------------------------------|----------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|

| Data transfer rate, max.                            |                                                                                                                | 710 kilobytes/second.                                                |

| Waveform transfer time, min.                        |                                                                                                                | 9 milliseconds for<br>1024 vertical and<br>512 pointer data.         |

| Waveform acquisition and transfer rate, max.        |                                                                                                                | 40 waveforms/second.                                                 |

| Typical                                             |                                                                                                                | 6-20 waveforms/second, depending on characteristics of input signal. |

| X-Y-Z analog display<br>outputs of waveform<br>data |                                                                                                                |                                                                      |

| X and Y                                             | 1 volt peak-to-peak into 100 kilohms or greater; adjustable from 0.75 to 1.3 volts.                            | 8-bit resolution.                                                    |

| Z                                                   | Zero volts (blanked),<br>1 volt (unblanked) into<br>100 kilohms or greater.<br>Blanked between data<br>points. |                                                                      |

| Z , X and Y out                                     |                                                                                                                | 50 ohms, +5%.                                                        |

| VERT IN, CAL IN,<br>TRIG IN (rear-panel<br>connectors) |

|--------------------------------------------------------|

|--------------------------------------------------------|

TABLE 1-1 (cont.)

| Characteristics                                        | Performance<br>Requirements                                                                                                                                                                                                      | Supplemental<br>Information              |

|--------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|

| z <sub>0</sub>                                         |                                                                                                                                                                                                                                  | 50 ohms, <u>+</u> 2%.                    |

| Attenuation of VERT IN/OUT and CAL IN/OUT signal paths |                                                                                                                                                                                                                                  | 0.33 dB at 400 MHz;<br>0.54 dB at 1 GHz. |

|                                                        | POWER SUPPLY                                                                                                                                                                                                                     |                                          |

| Remote control                                         |                                                                                                                                                                                                                                  |                                          |

| ACUTATE                                                | TTL low level (<0.8V) applied between center conductor and outer conductor turns on power supply. A return to a TTL high level (>2V) turns off power supply. Outer conductor is isolated from chassis by approximately 100 ohms. |                                          |

| ENABLE                                                 | Provides TTL low level (<0.4V) between center conductor and outer conductor approximately 150 milliseconds after power-up. Maximum sink current is 16 milliamps. Goes to TTL high level after power supply is                    |                                          |

turned off.

TABLE 1-1 (cont.)

| Characteristics                              | Performance<br>Requirements | Supplemental<br>Information |  |

|----------------------------------------------|-----------------------------|-----------------------------|--|

|                                              | POWER INPUT                 |                             |  |

| Line voltage                                 |                             |                             |  |

| 115, nominal                                 |                             | 90 to 132 volts AC.         |  |

| 230, nominal                                 |                             | 180 to 250 volts AC.        |  |

| Line frequency                               |                             | 48 to 440 Hz.               |  |

| Power consumption                            |                             |                             |  |

| Typical, not including plug-ins              |                             | 250 watts                   |  |

| Maximum, including plug-ins                  |                             | 360 watts                   |  |

| Line current, max                            |                             | 5.2 amps (90 VAC)           |  |

|                                              | SAFETY                      |                             |  |

| Power line fuse 6 amps, 250 volt, fast-blow. |                             |                             |  |

TABLE 1-2

7912AD SYSTEM ELECTRICAL CHARACTERISTICS

| Plug-in<br>Amplifier | Performance<br>Feature                           | Minimum<br>Deflection<br>Factor | Bandwidth                                        | Rise Time<br>(Calculated)                      | Relative<br>Accuracy |

|----------------------|--------------------------------------------------|---------------------------------|--------------------------------------------------|------------------------------------------------|----------------------|

| 7A11                 | Low-capacitance<br>FET probe<br>built-in         | 5 mV/div                        | 250 MHz<br>(225 MHz,<br>+30 to +40<br>degrees C) | 1.4 ns<br>(1.6 ns,<br>+30 to +40<br>degrees C) | 2%                   |

| 7A13                 | Differential input; DC offset                    | 1 mV/div                        | 105 MHz                                          | 3.4 ns                                         | 1.5%                 |

| 7A16A                | 1-megohm input                                   | 5 mV/div                        | 225 MHz                                          | 1.6 ns                                         | 2%                   |

| 7A16P                | Programmable                                     | 10 mV/div                       | 200 MHz                                          | 1.8 ns                                         | 2%                   |

| 7 <b>A</b> 18        | Dual-channel,<br>1-megohm input                  | 5 mV/div                        | 75 MHz                                           | 4.7 ns                                         | 2%                   |

| 7A19                 | Wide bandwidth,<br>50-ohm input                  | 10 mV/div                       | 500 MHz<br>(400 MHz,<br>+30 to +40<br>degrees C) | 0.8 ns<br>(0.9 ns<br>+30 to +40<br>degrees C)  | 3%                   |

| 7A24                 | Dual-channel,<br>wide bandwidth,<br>50-ohm input | 5 mV/div                        | 350 MHz<br>(300 MHz,<br>+30 to +40<br>degrees C) | 1.0 ns<br>(1.2 ns,<br>+30 to +40<br>degrees C) | 2%                   |

| 7A21N                | Direct access,<br>50-ohm input                   | Less than 4 V/div               | 1 GHz                                            | 0.35 ns                                        |                      |

| 7A26                 | Dual-channel<br>1-megohm input                   | 5 mV/div                        | 200 MHz<br>(160 MHz,<br>+30 to +40<br>degrees C) | 1.8 ns<br>(2.2 ns, +30<br>to +40<br>degrees C) | 2%                   |

<sup>\*</sup>Applies to all deflection factors when the plug-in gain is set at the

deflection factor designated on each plug-in. The calibration signal must be supplied by an external calibrator whose accuracy is within 0.25%.

TABLE 1-3

RECOMMENDED TIME BASE PLUG-IN

| Plug-in        | Maximum<br>Sweep Rate | Triggering Frequency Range | Notes                                                                    |

|----------------|-----------------------|----------------------------|--------------------------------------------------------------------------|

| 7B80           | 1 ns/div              | 400 MHz                    |                                                                          |

| 7B80<br>MOD GB | 500 ps/div            | 400 MHz                    | Slowest sweep rate is<br>10 us/div                                       |

| 7B90P          | 500 ps/div            | 400 MHz                    | Programmable                                                             |

| 7B92A          | 500 ps/div            | 500 MHz                    | Both normal and delayed sweep; set intensity carefully in alternate mode |

TABLE 1-4

ENVIRONMENTAL CHARACTERISTICS

| Characteristics                                                                            | Description                                                                                                                                                                                        |  |

|--------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Temperature                                                                                |                                                                                                                                                                                                    |  |

| Operating                                                                                  | 0 to +40 degrees C.                                                                                                                                                                                |  |

| Nonoperating                                                                               | -55 to +75 degrees C.                                                                                                                                                                              |  |

| Altitude                                                                                   |                                                                                                                                                                                                    |  |

| Operating                                                                                  | Up to 4570 meters (15,000 feet).                                                                                                                                                                   |  |

| Nonoperating                                                                               | Up to 15,200 meters (50,000 feet).                                                                                                                                                                 |  |

| Electromagnetic compatibility (EMC) with plug-ins or EMC-shielded blank plug-ins installed | Meets all applicable parts of MIL-STD-461A when tests are performed according to MIL-STD-462 for radiated and conducted electromagnetic emissions and susceptibility from 30 hertz to 1 gigahertz. |  |

TABLE 1-5

PHYSICAL CHARACTERISTICS

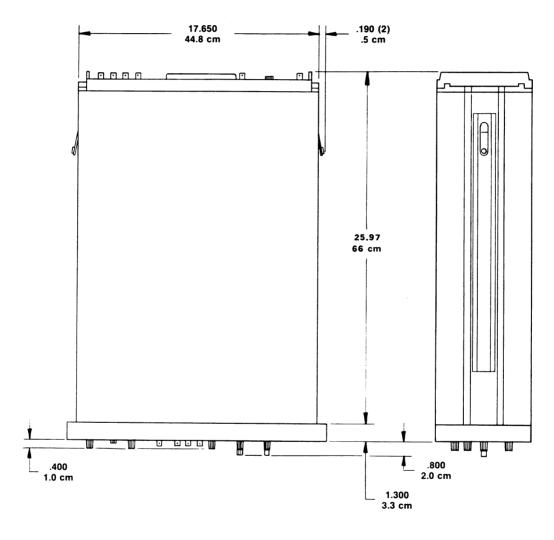

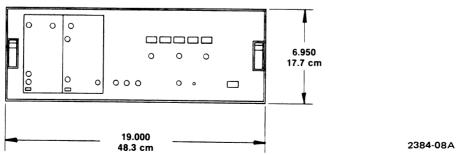

| Characteristics      | Description  Can be mounted in standard 19-inch rack. See Fig. 1-6.                                                                           |  |

|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|--|

| Size                 |                                                                                                                                               |  |

| Weight (no plug-ins) | Approximately 24.7 kilograms (54.6 pounds).                                                                                                   |  |

| Air intake at fan    | 2.83 meters <sup>3</sup> /min.<br>(100 feet <sup>3</sup> /min), max; typically<br>2.40 meters <sup>3</sup> /min. (85 feet <sup>3</sup> /min). |  |

## Accessories

The following accessories are supplied with the 7912AD; for part numbers, see the Accessories page in the back of Vol. II.

- 1 power cord, 2.4 meters (8 feet)

- 1 set of rack slides with hardware

- 1 IEEE 488 bus cable, 2 meters (6.6 feet)

- 1 operators manual

- 1 service manual (two volumes)

Checkout software with manual

FIG. 1-6. 7912AD outside dimensions shown in both inches and centimeters.

## SECTION 2

## **OPERATION**

This section contains a description of 7912AD controls and connectors and instructions for local (operator) control of the instrument. For more complete operating and programming instructions, refer to the 7912AD Operator's manual.

The 7912AD is based on the TEKTRONIX 7000-series plug-in concept. Signal-conditioning plug-ins are used. These have their own operating controls; see the plug-in operators manuals for a description of the controls and instructions for operating the plug-ins. Although some of the plug-in controls are referenced in this manual, they are not fully described, nor are full instructions for their use provided.

## Controls and Connectors

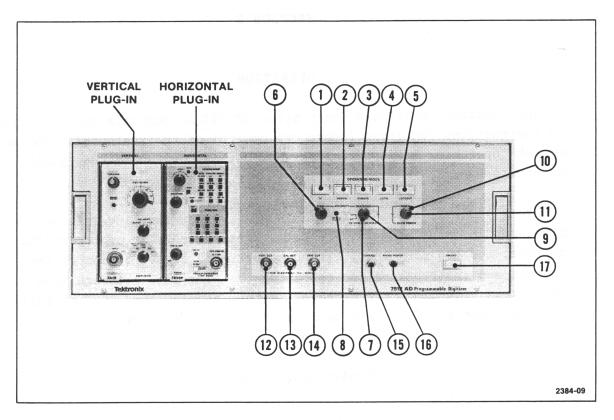

#### Front Panel

The front panel controls and connectors are shown in Fig. 2-1. The numbers in the following descriptions refer to Fig. 2-1.

#### OPERATING MODE

- (1) TV: Sets the 7912AD to TV mode. Lights when in TV mode. If, when the TV button is pressed, the 7912AD is performing a digitize operation, it waits until completed before switching to TV mode.

- (2) DIGITAL: Sets the 7912AD to digital mode and initiates a digitize operation. Lights when in digital mode. There is a two-second delay for set-up when switching from TV to digital mode. Once DIGITAL is pressed, the 7912AD is readied to digitize but waits for a sweep gate from the time base to store data detected on the target. To be detected, the input waveform and/or graticule must have been written on the target with sufficient intensity (set by the INTENSITY controls).

Fig. 2-1. Front panel controls and connectors. The numbers refer to descriptions in the text of the controls and connectors.

- 3 REMOTE: Lights to indicate when the 7912AD is set to remote mode by the IEEE 488 bus system controller. When REMOTE is pressed, the 7912AD requests service from the IEEE 488 bus controller if the interrupt is enabled.

- 4 LOCAL: Returns the 7912AD from remote mode to local control if not in remote with lockout state (see LOCKOUT). Lights when in local mode. If the instrument is executing a remote command or performing a digitize operation, it waits until finished to return to local.

- 5 LOCKOUT: Lights to indicate the 7912AD is set to either local with lockout state or remote with lockout state by the IEEE 488 bus system controller. In remote with lockout state (both REMOTE and LOCKOUT are lighted), the LOCAL button does not return the instrument from remote to local control.

#### INTENSITY

- 6 MAIN: Sets writing beam intensity to control input waveform definition on the converter tube target.

- 7 GRATICULE: Sets writing beam intensity when the graticule is written on the converter tube target (outer knob). When set to minimum, the graticule is not written, so it is not displayed (TV mode) or digitized (digital mode).

#### DECREASE INTENSITY

8 Lights to warn that the 6800 MPU is automatically limiting beam current because either or both intensity controls are set too high. Also lights when the MPU turns off the writing beam because it detects an invalid sweep rate. Blinks when a hardware protection circuit becomes active; in this condition, the beam is automatically deflected outside the graticule area.

# (9) TV SCALE FACTORS

Turns on or off the display of scale factors when in TV mode (inner knob).

# (10) FOCUS

Sets focus of writing beam to affect trace definition (outer knob).

# 11) BEAM FINDER

Compresses the input waveform into the graticule area, even if the waveform is overdriving the 7912AD input (inner button). Used to determine how the plug-in controls should be changed to match the input waveform. Can not be set under remote control.

- (12) VERT OUT

- Connects through 50-ohm coaxial cable to rear panel VERT IN.

- (13) CAL OUT

Connects through 50-ohm coaxial cable to rear panel CAL IN.

(14) TRIG OUT

Connects through 50-ohm coaxial cable to rear panel TRIG IN.

(15) GROUND

Connects to chassis ground.

(16) PROBE POWER

Provides power for TEKTRONIX active probes.

(17) ON/OFF

Turns on/off the 7912AD power supply if the rear-panel PRINCIPAL POWER SWITCH is on (can be overridden by rear-panel ACTUATE connector). Lights when the power supply is turned on.

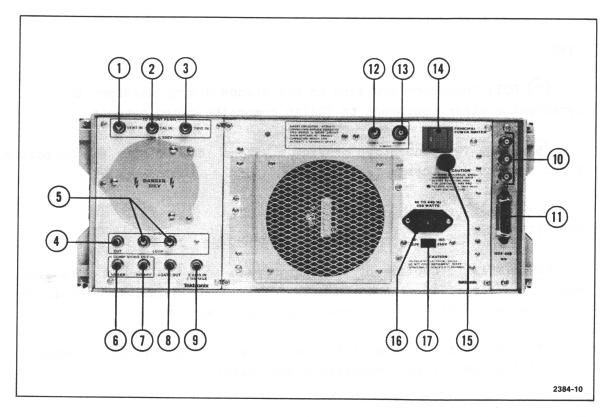

## Rear Panel

The rear panel controls and connectors are shown in Fig. 2-2. The numbers in the following descriptions refer to Fig. 2-2.

Fig. 2-2. Rear panel controls and connectors. The numbers refer to descriptions in the text of the controls and connectors.

# 1) VERT IN

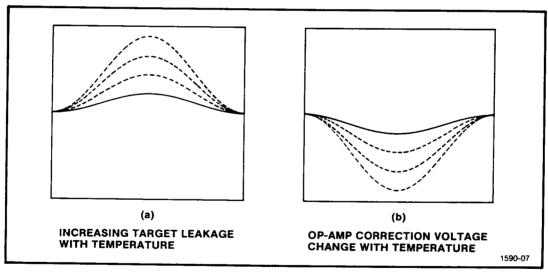

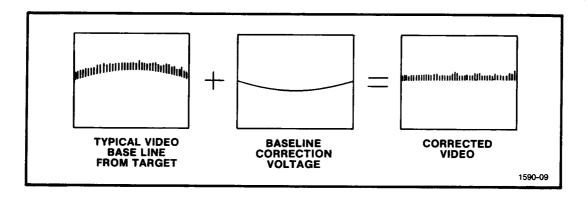

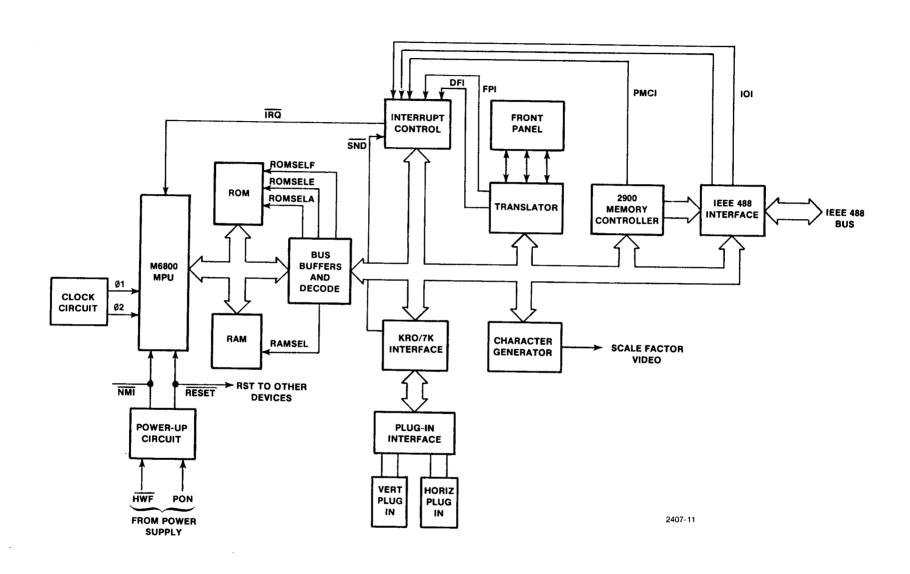

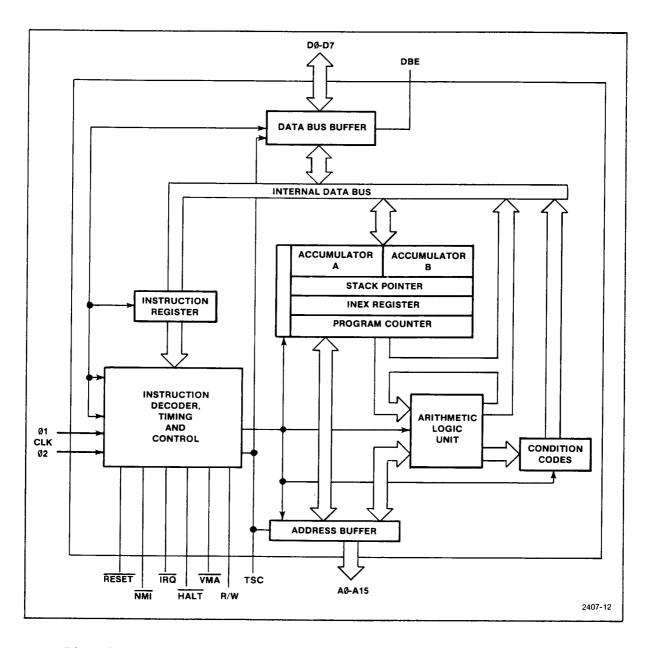

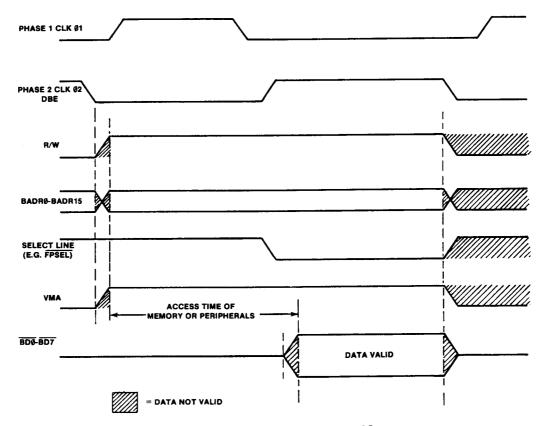

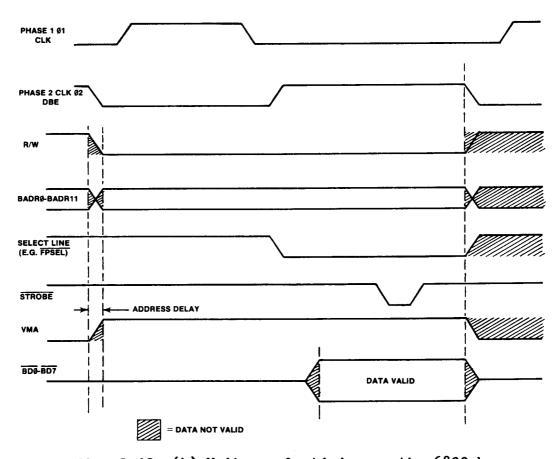

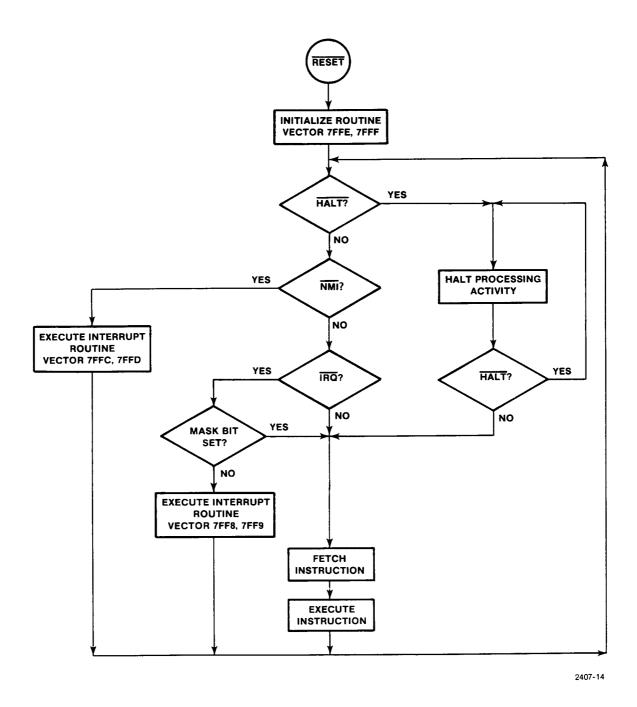

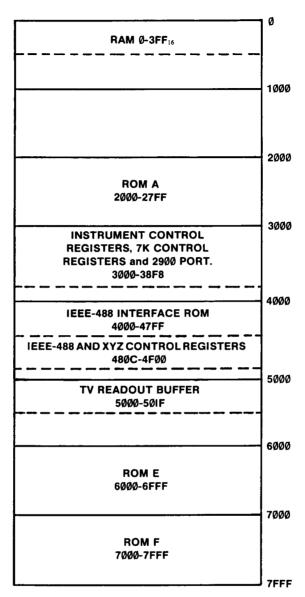

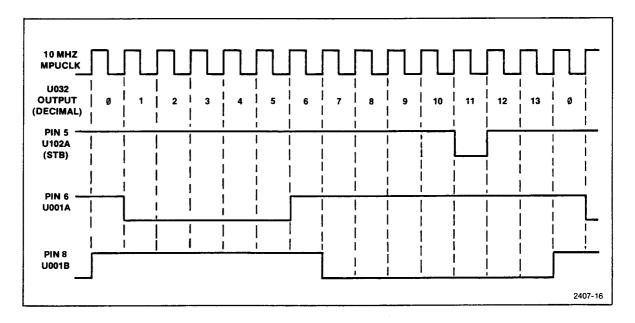

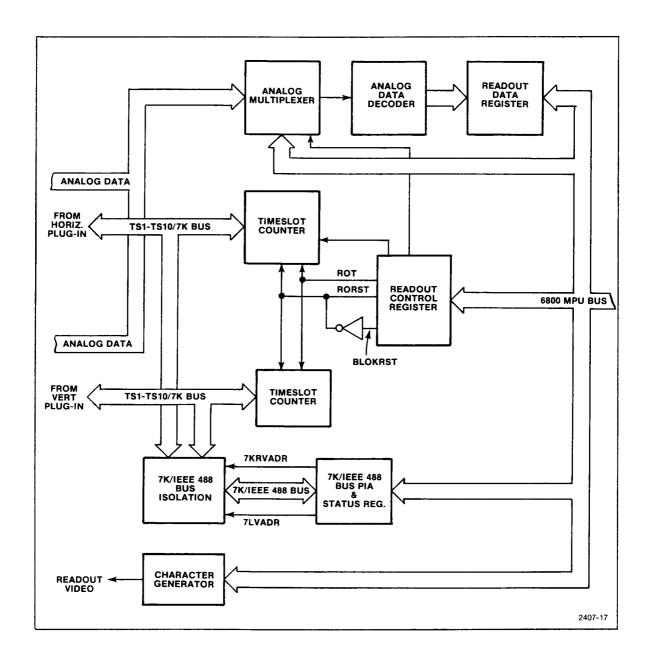

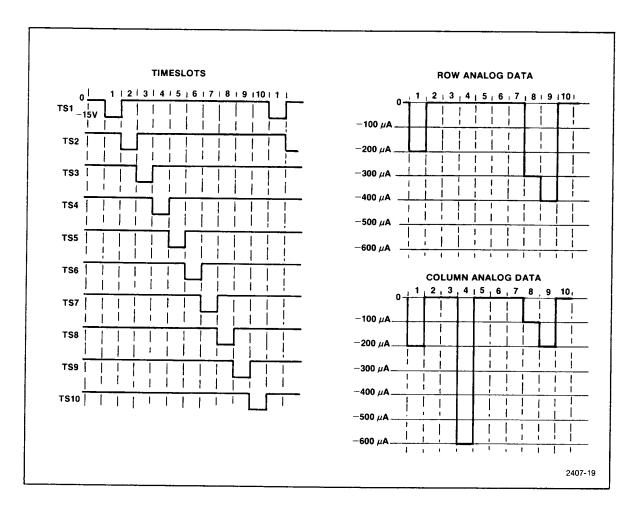

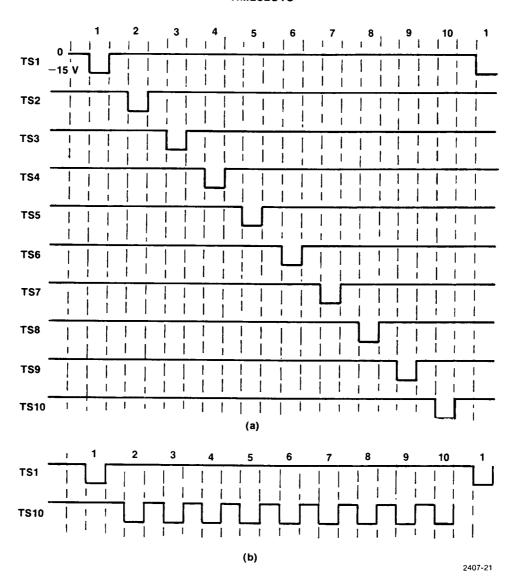

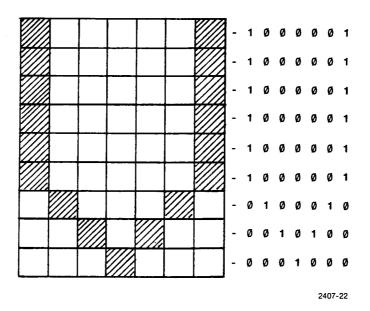

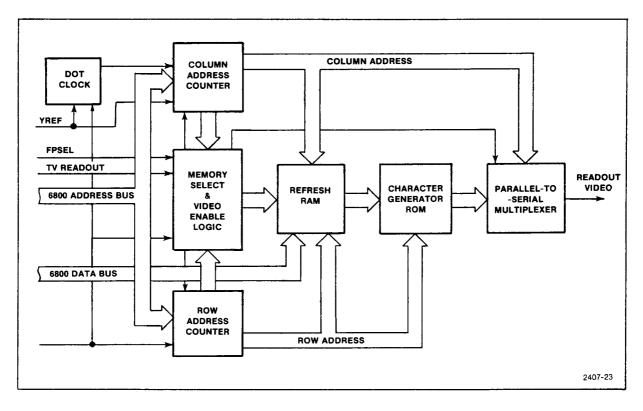

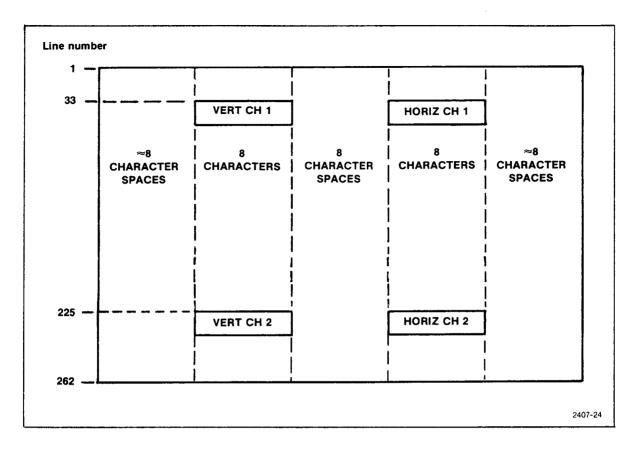

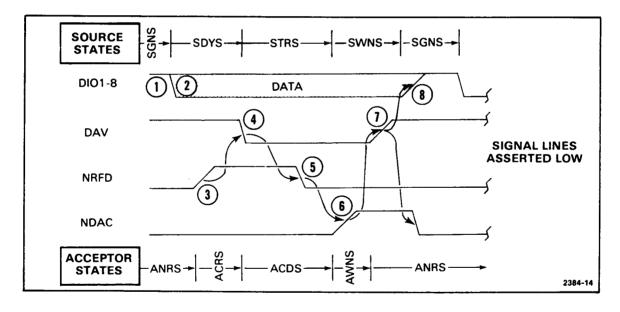

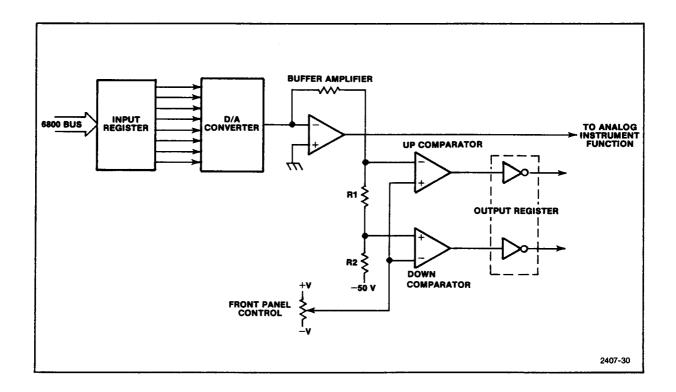

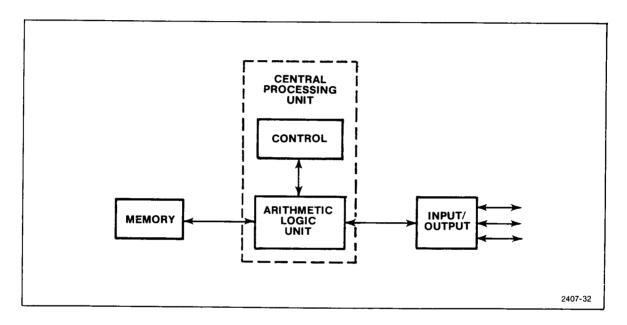

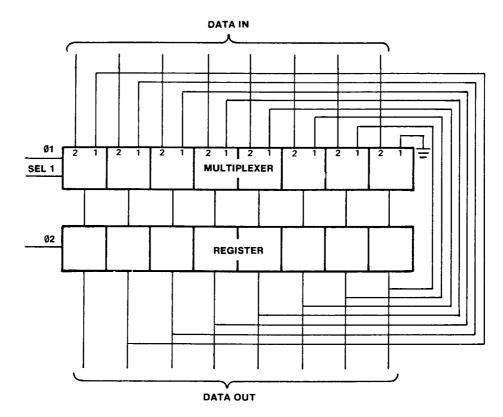

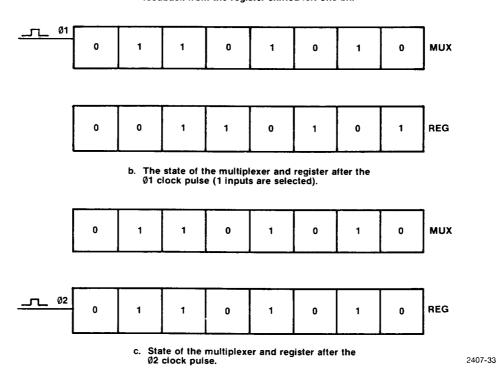

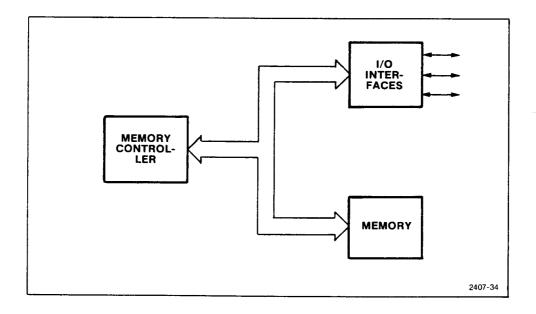

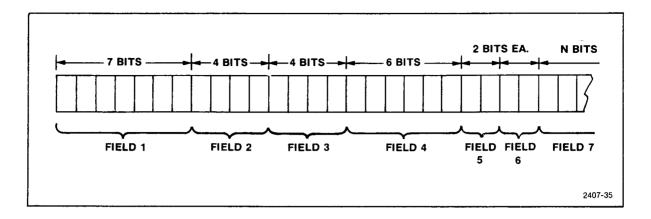

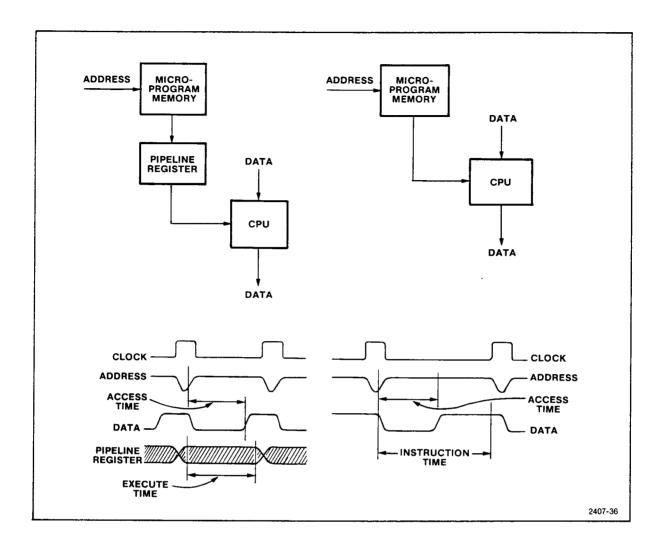

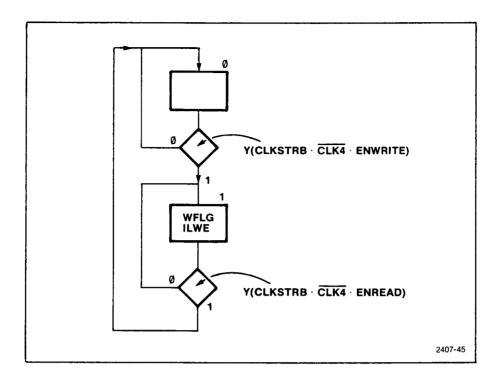

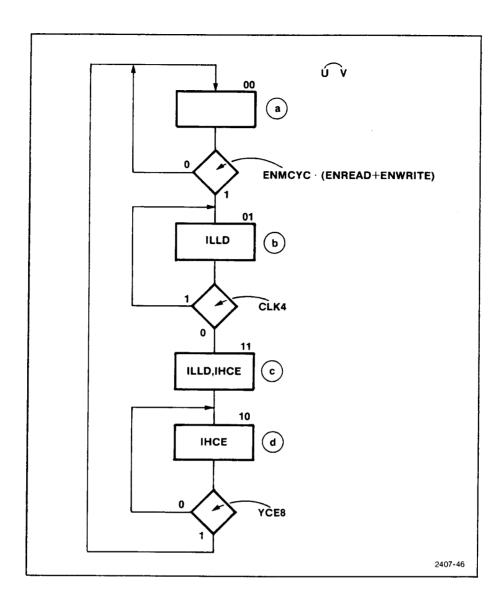

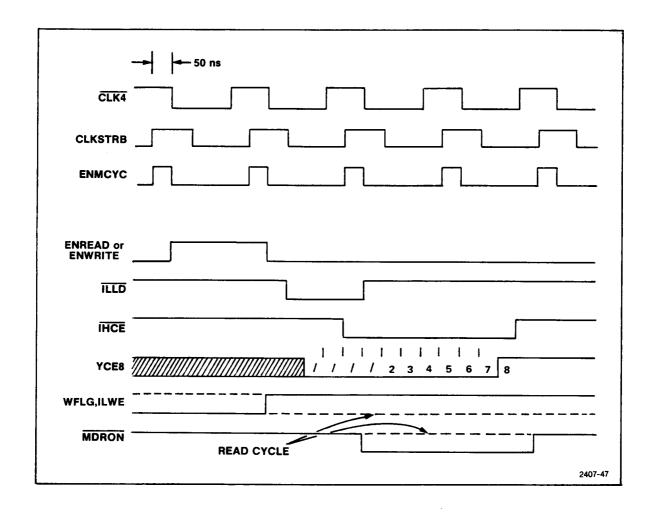

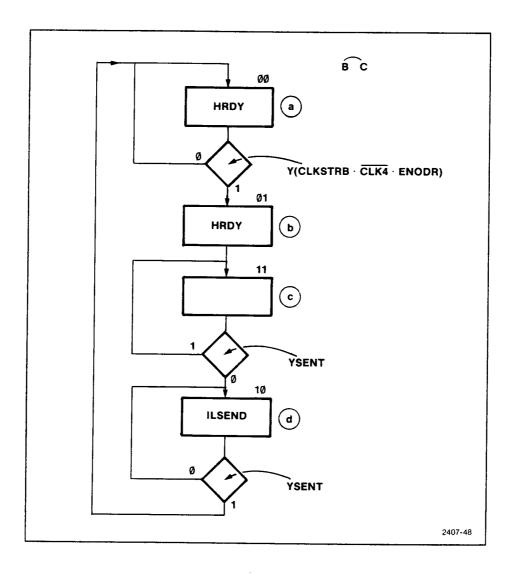

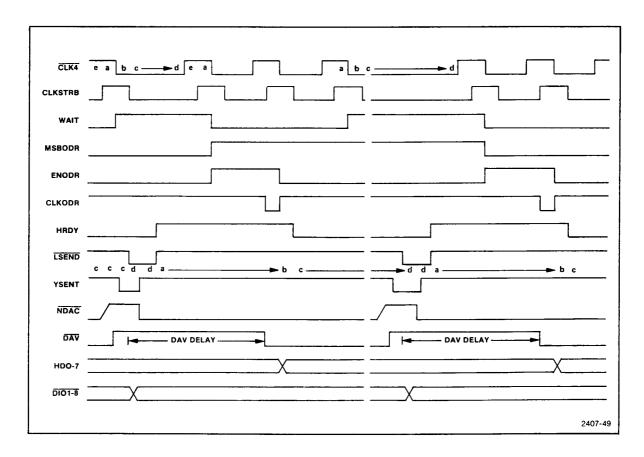

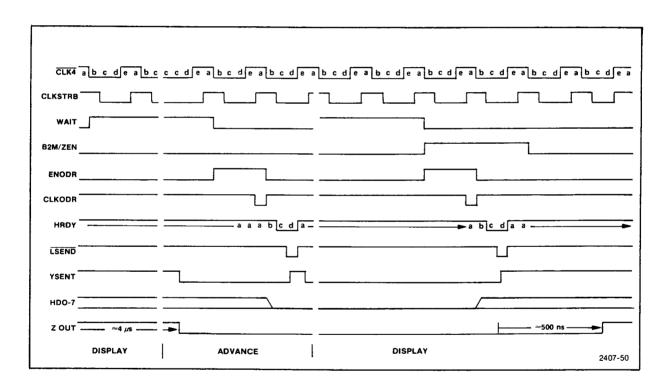

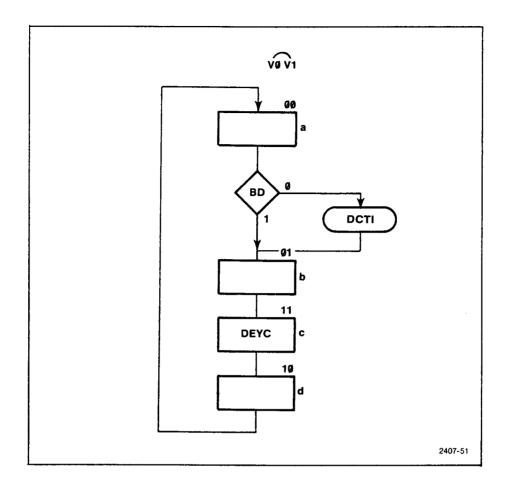

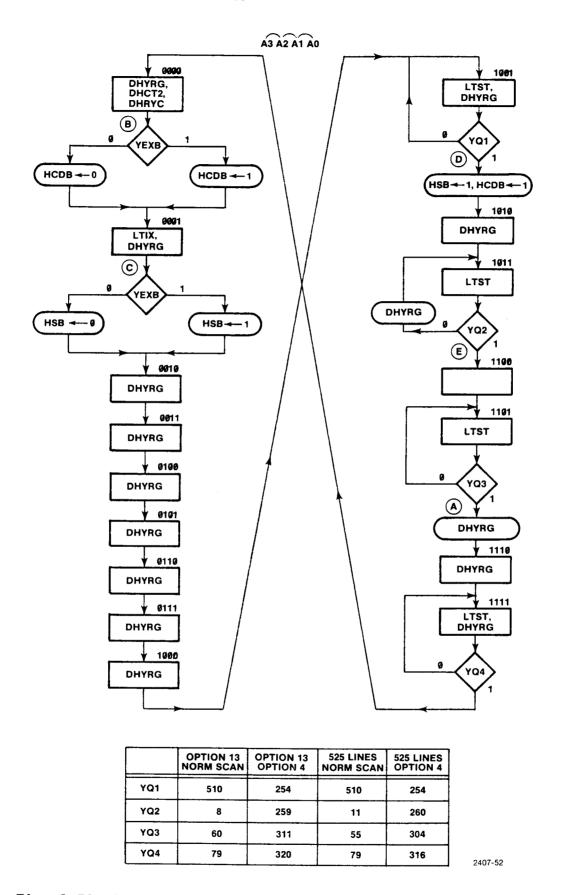

Connects through 50-ohm coaxial cable to front panel VERT OUT.